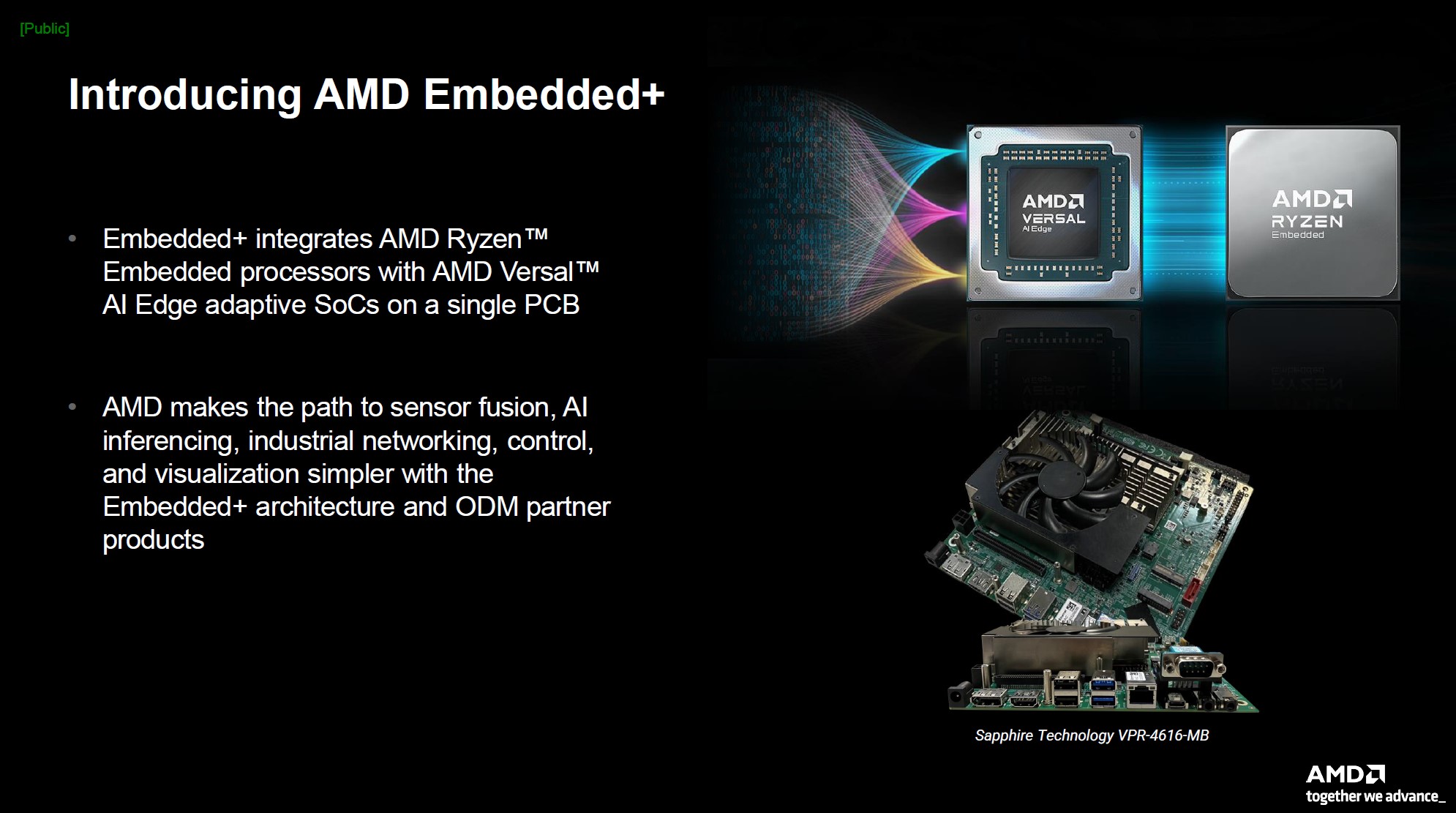

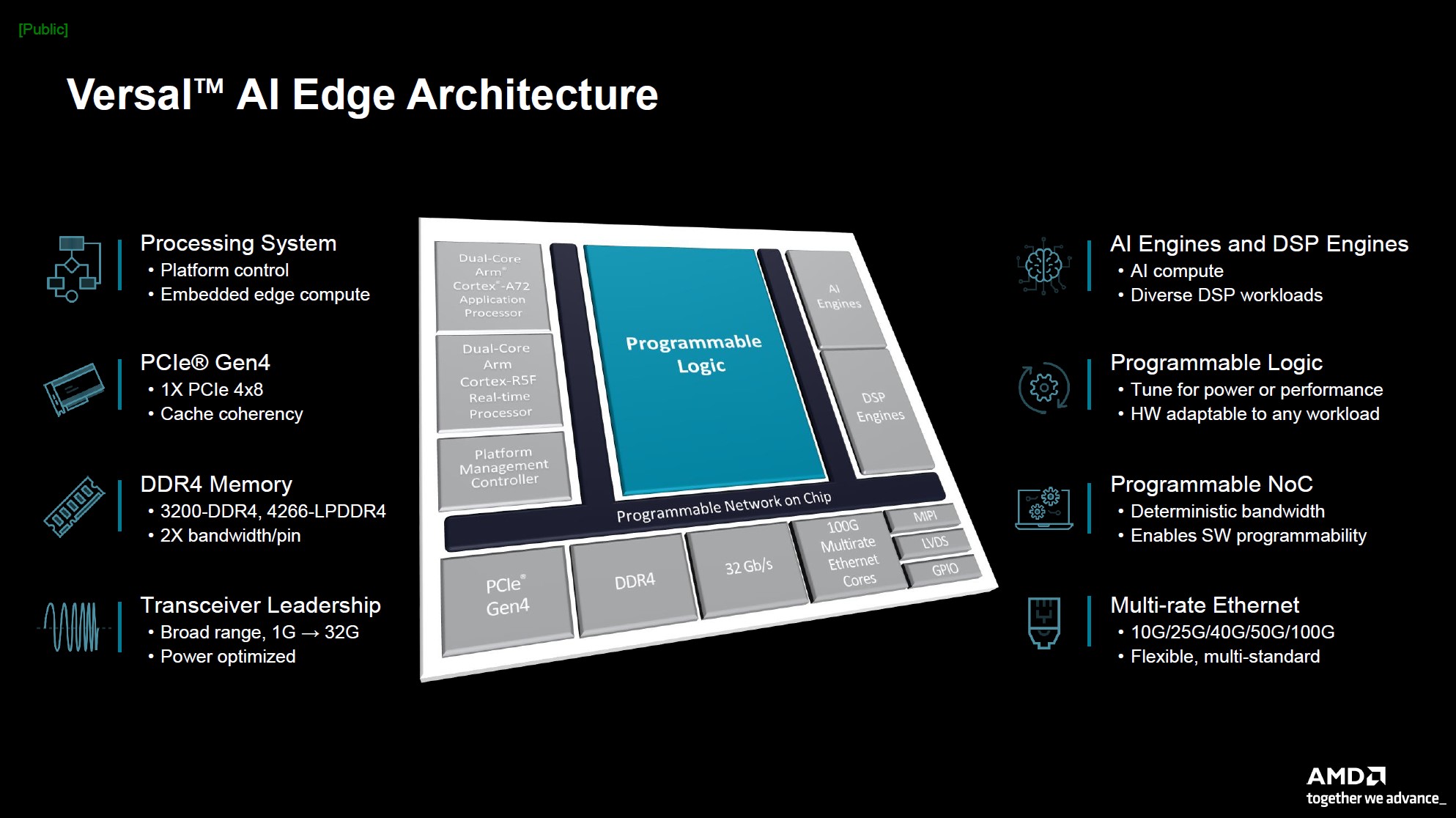

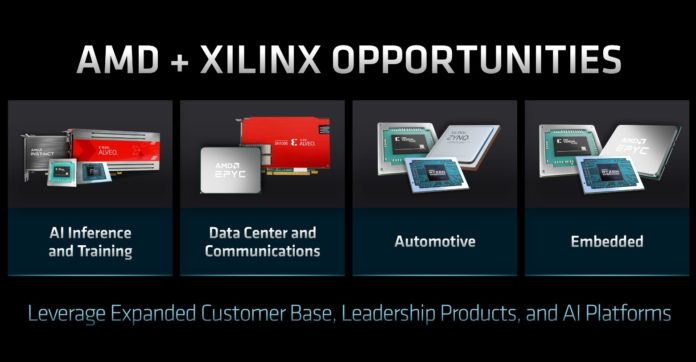

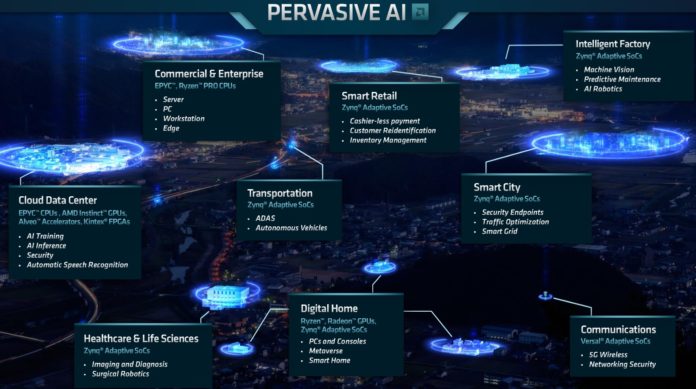

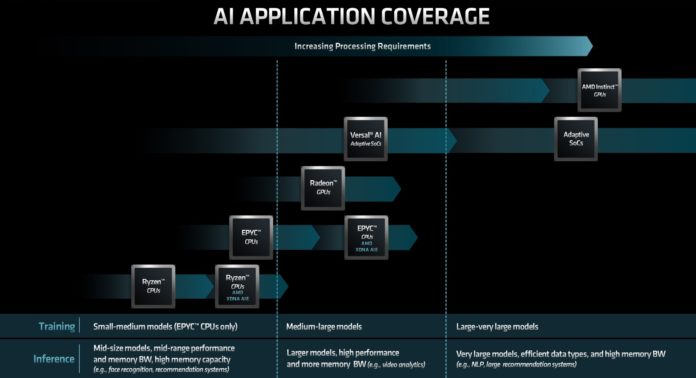

AMD-Xilinx and AI Updates at AMD Financial Analyst Day 2022

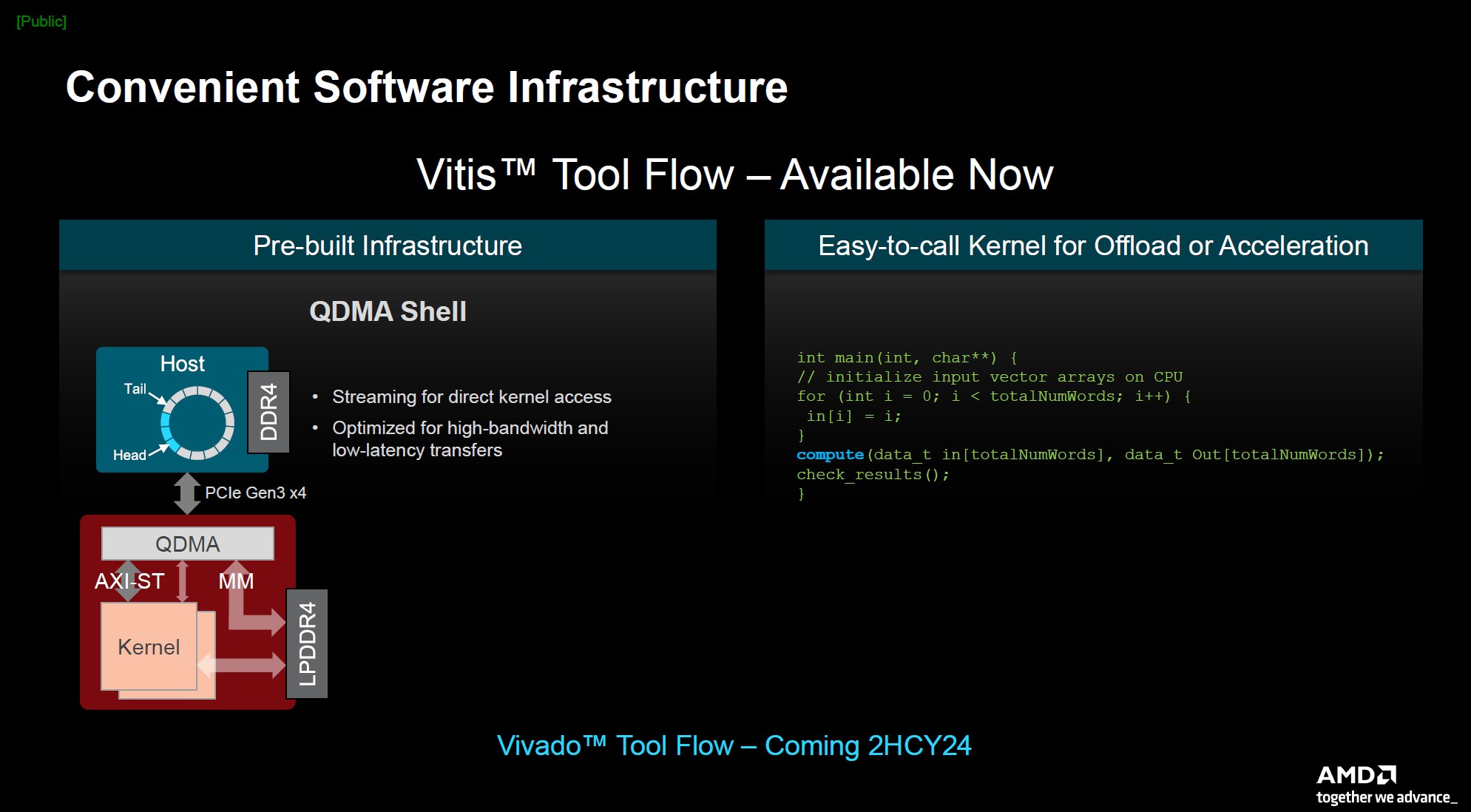

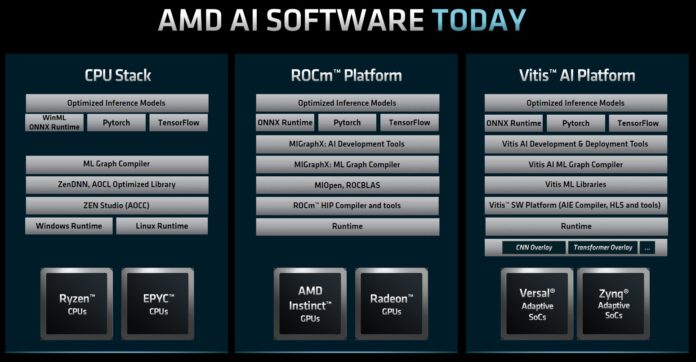

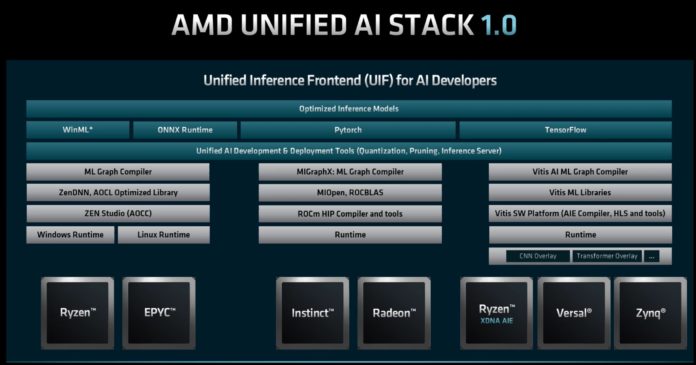

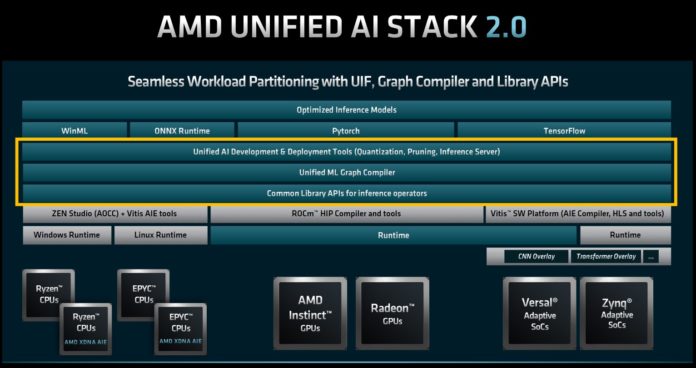

e claro o software integrando tudo no ROCm

https://www.servethehome.com/amd-xilinx-ai-updates-at-amd-financial-analyst-day-2022/

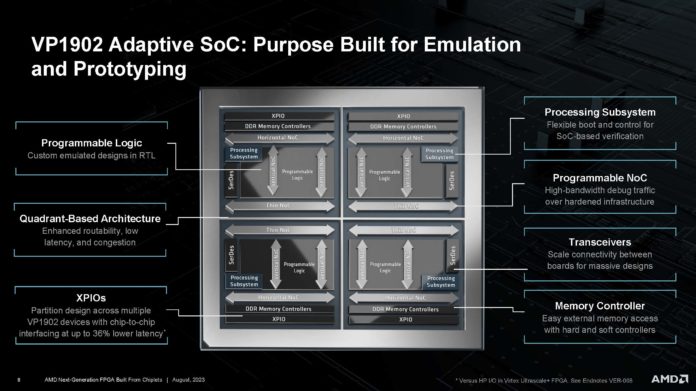

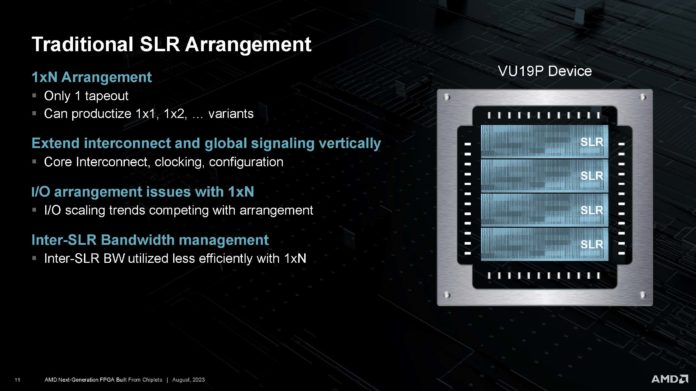

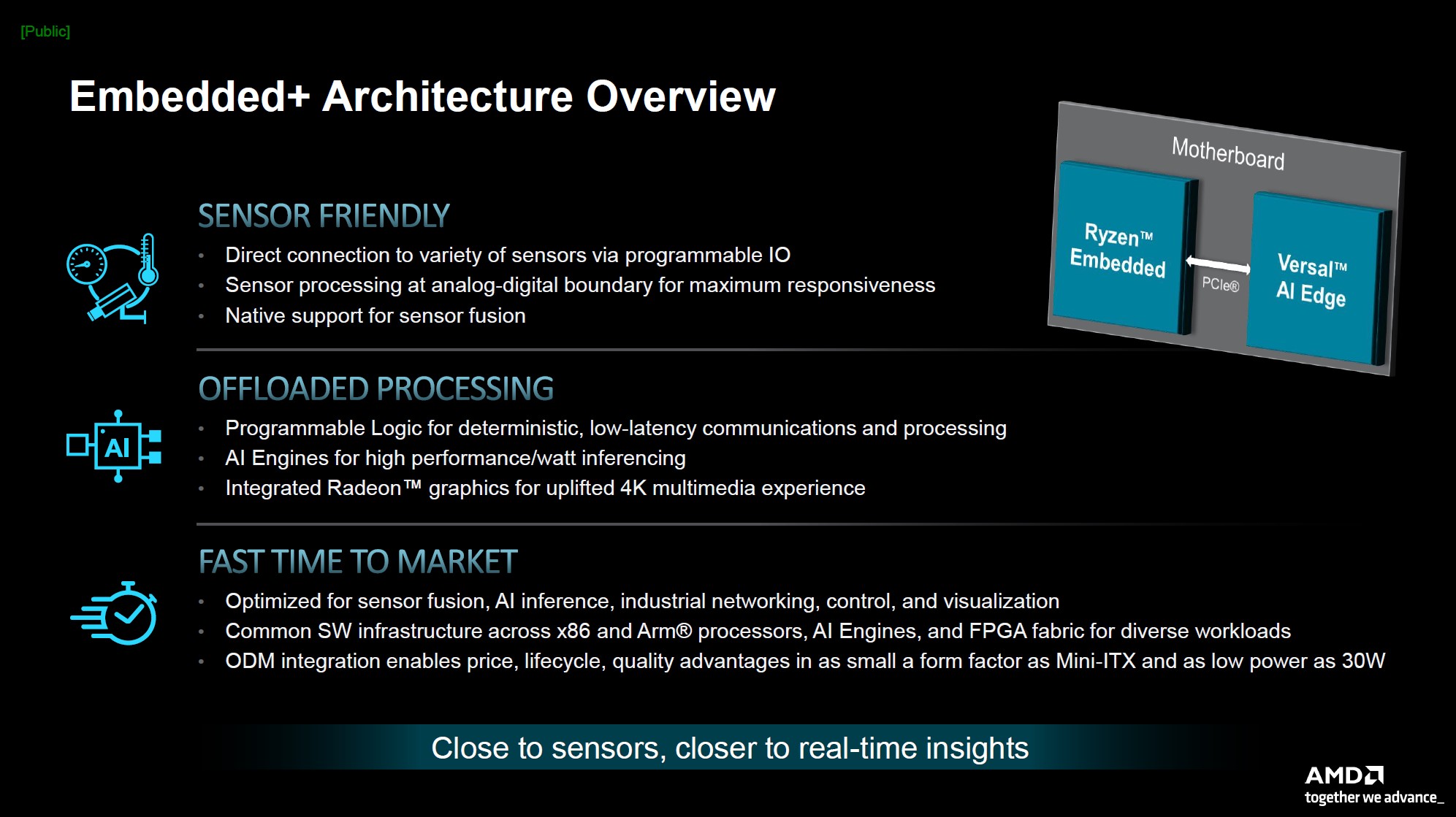

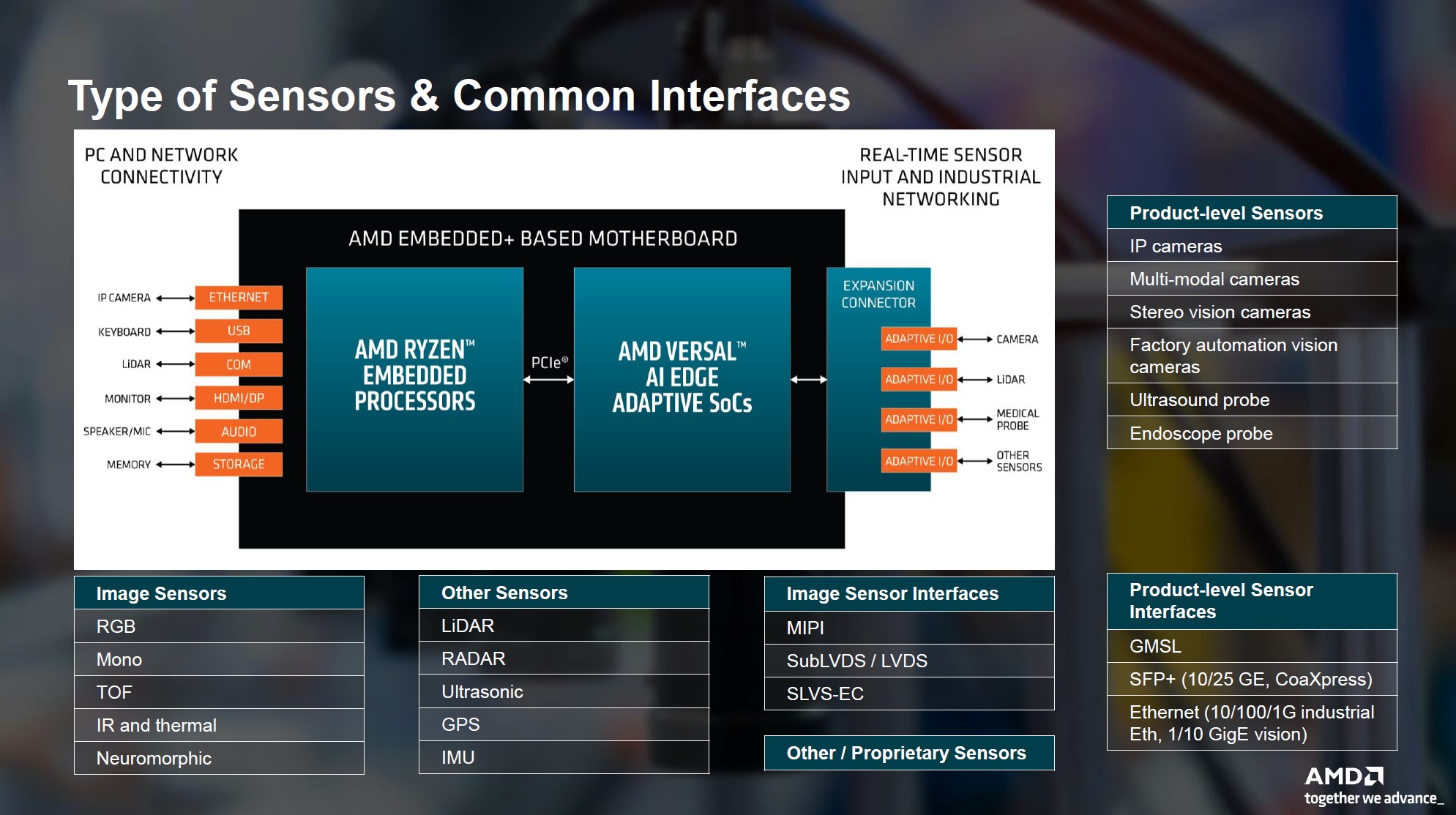

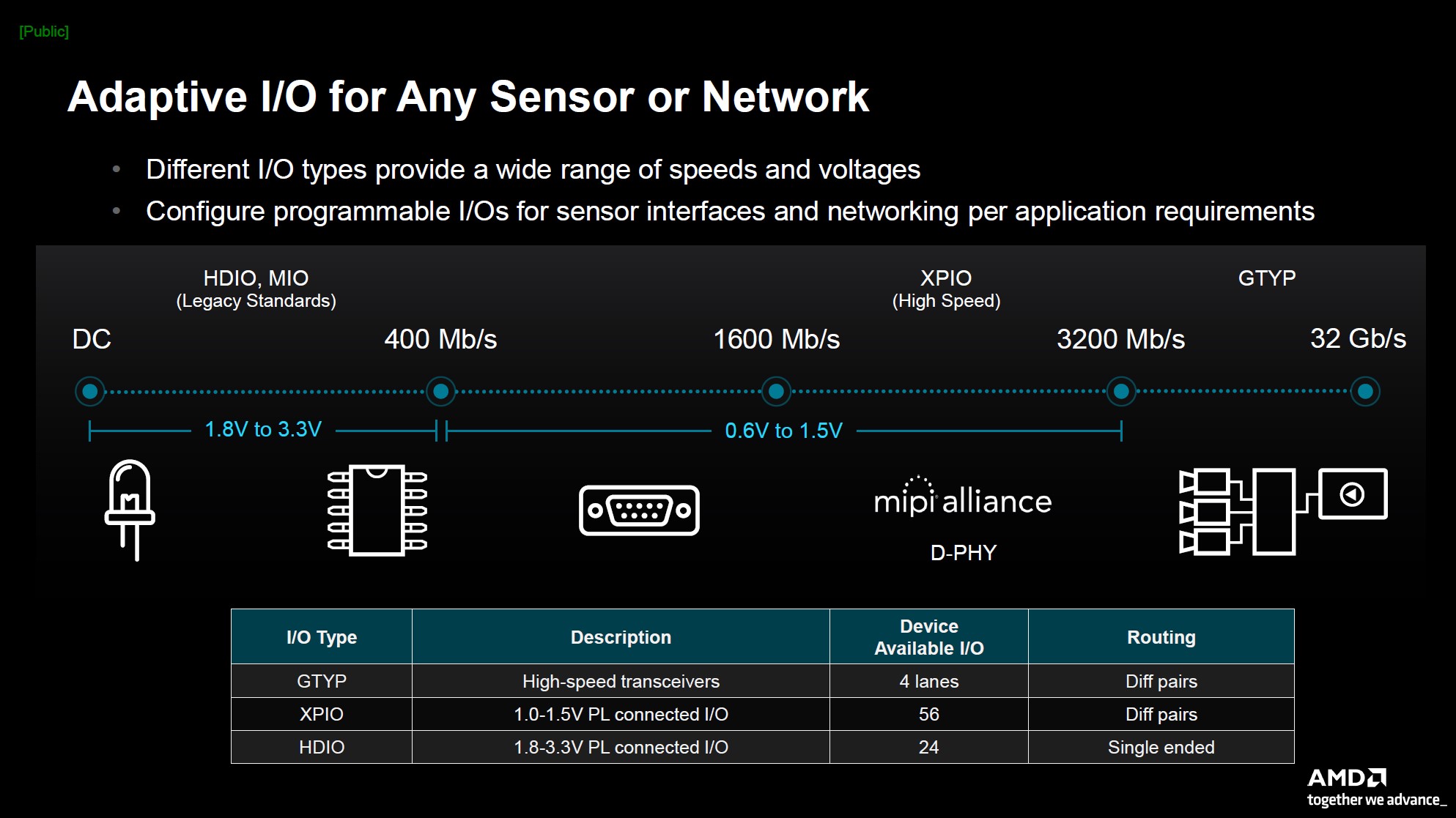

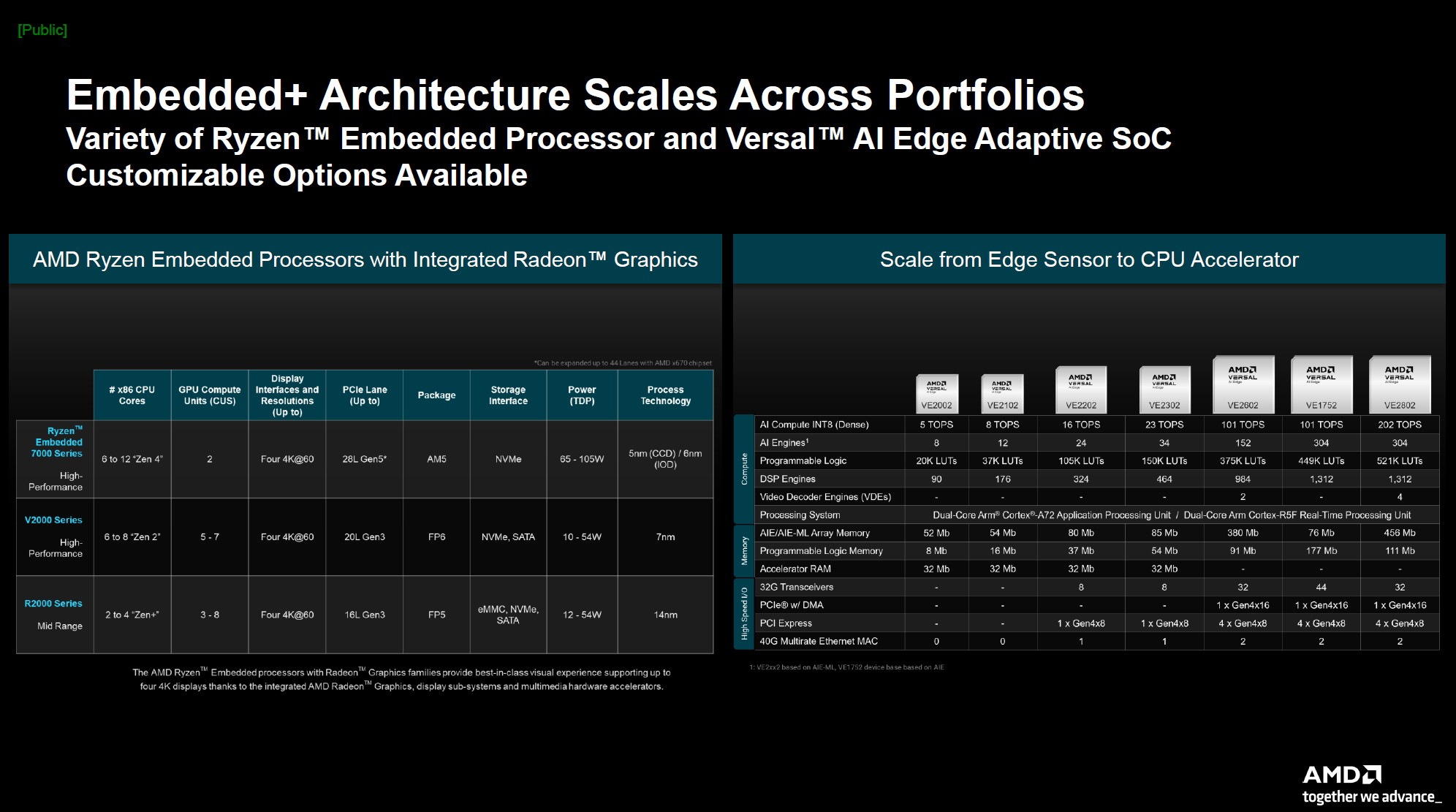

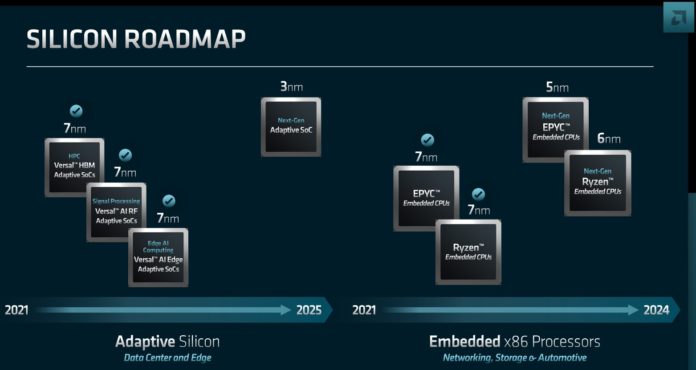

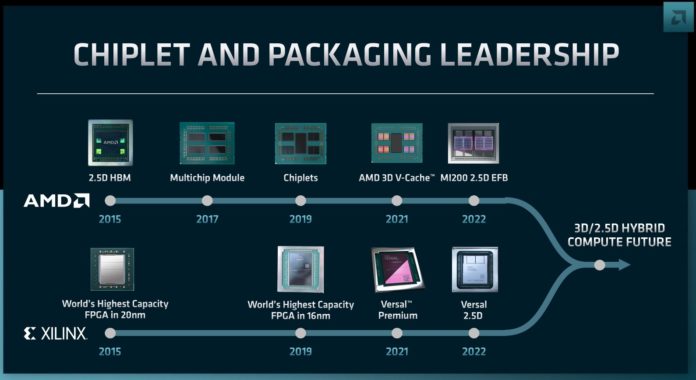

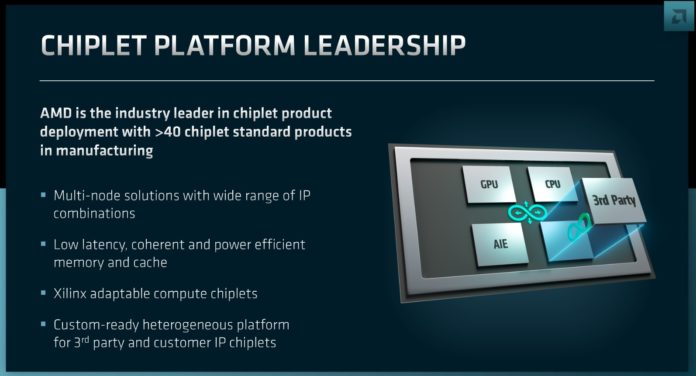

por outro lado a convergência dos modelos chiplets, quer da Xilinx quer da AMD, e do "xPU interconnect"

AMD Technology Roadmap from AMD Financial Analyst Day 2022

https://www.servethehome.com/amd-technology-roadmap-from-amd-financial-analyst-day-2022/