_SkyWaLKeR_

Power Member

Depende dos jogos... Penso que nakeles que usam o Raytracing essencialmente para as sombras a AMD ta ao mesmo nível k a nvidia... Penso que o problema da AMD seja quando dão uso forte ao Raytracing para iluminação...

https://www.digitimes.com/news/a20210331PD215.htmlGraphics card makers expect their supply to remain constrained through the end of this year, due to shortages of chips and components, and are encouraged to raise their prices.

AMD on April 1st published a new patent application that seems to show the way its chiplet GPU design is moving towards. Before you say it, it's a patent application; there's no possibility for an April Fool's joke on this sort of move. The new patent develops on AMD's previous one, which only featured a passive bridge connecting the different GPU chiplets and their processing resources. If you want to read a slightly deeper dive of sorts on what chiplets are and why they are important for the future of graphics (and computing in general), look to this article here on TPU.

The new design interprets the active bridge connecting the chiplets as a last-level cache - think of it as L3, a unifying highway of data that is readily exposed to all the chiplets (in this patent, a three-chiplet design). It's essentially AMD's RDNA 2 Infinity Cache, though it's not only used as a cache here (and for good effect, if the Infinity Cache design on RDNA 2 and its performance uplift is anything to go by); it also serves as an active interconnect between the GPU chiplets that allow for the exchange and synchronization of information, whenever and however required. This also allows for the registry and cache to be exposed as a unified block for developers, abstracting them from having to program towards a system with a tri-way cache design. There are also of course yield benefits to be taken here, as there are with AMD's Zen chiplet designs, and the ability to scale up performance without any monolithic designs that are heavy in power requirements. The integrated, active cache bridge would also certainly help in reducing latency and maintaining chiplet processing coherency.

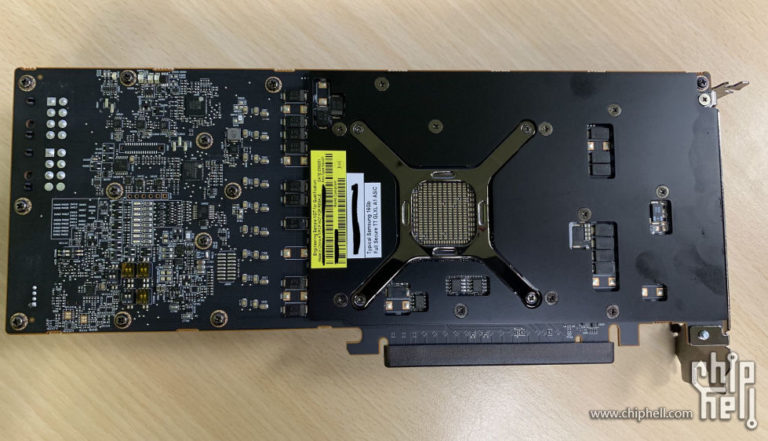

https://videocardz.com/newz/amd-rad...ard-with-navi-21-gpu-and-16gb-memory-picturedOne of the labels reveals that the card is ‘Full Secure TT GLXL’ model. There have been leaks on Navi 21 GLXL before and this is without a doubt a next-generation model. What we do not know is how many Stream Processors does this variant has.

The card is also the first blower-type Navi 2X graphics card from AMD, which is kept in dual-slot design, unlike AMD’s gaming RX6800XT/6900XT models. This certainly affects thermal performance and heat exchange capacity. A cut-down GPU with reduced clocks should fit under 250W of typical board power though.

A 6700 XT realmente não vale os 480$ de MRSP. Nem de perto.

Alguem aqui já alguma vez comprou algo na loja oficial da AMD?

Vende, acho que vem da Irlanda não tenho a certeza, mas sei que enviam de dentro da UE.

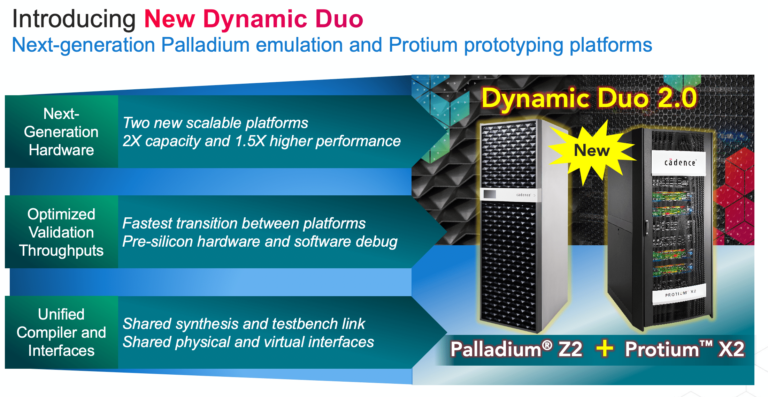

Cadence calls their hardware acceleration platforms, Palladium Z2 for fast pre-silicon hardware debug and Protium X2 for fast pre-silicon software validation, their Dynamic Duo. With good reason. Hardware acceleration is now fundamental to managing the complexity of verification and validation for large systems, hardware and software.

https://semiwiki.com/eda/297771-cadence-dynamic-duo-upgrade-debuts/All sounds good, who has signed up? AMD and NVIDIA have publicly endorsed both platforms and Arm has publicly endorsed Palladium Z2.