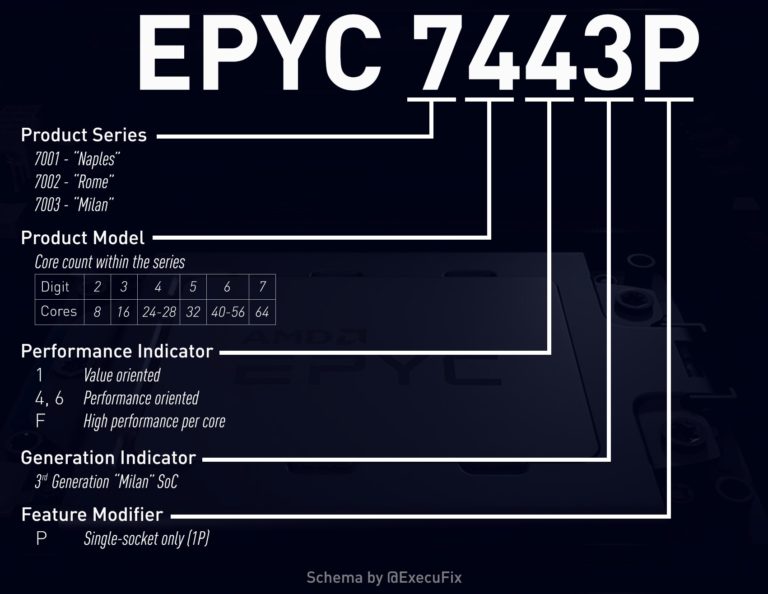

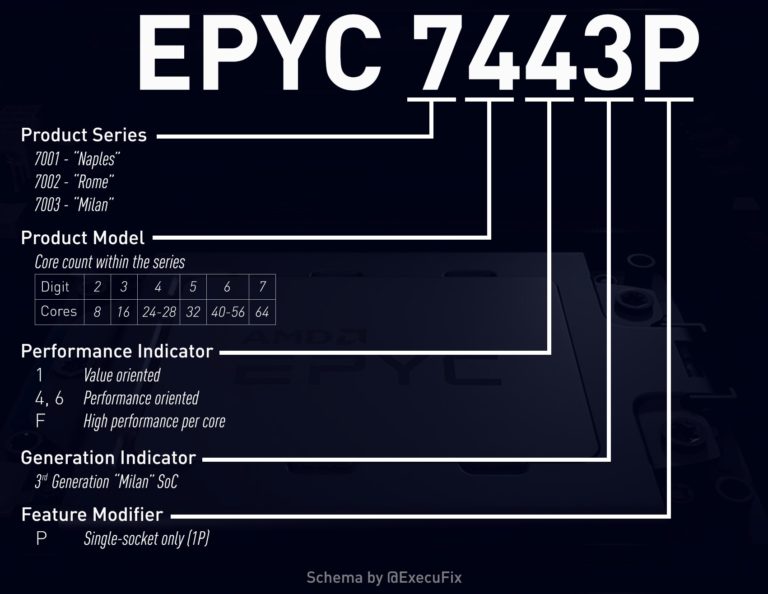

@Nemesis11 parece que um tuitteiro já conseguiu descodificar os nomes dos Epyc Milan

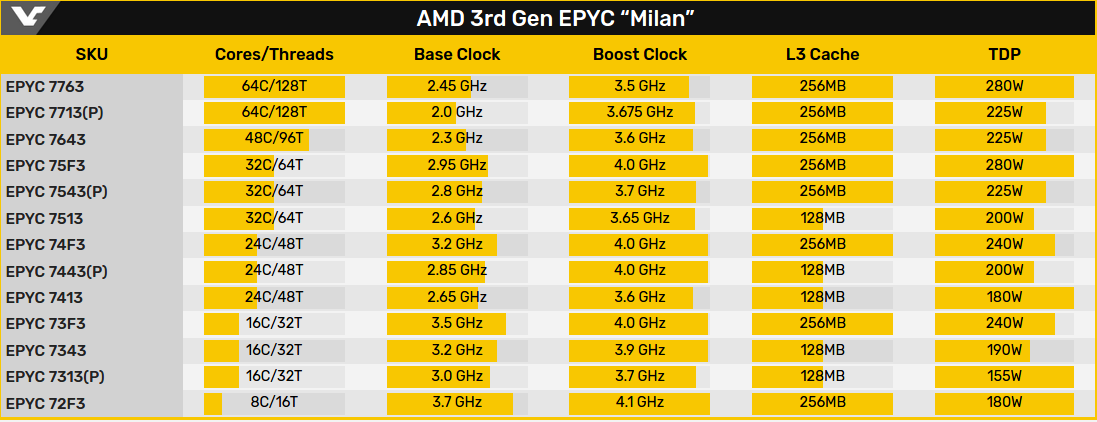

o que daria qualquer coisa como isto

https://videocardz.com/newz/amd-3rd-gen-epyc-milan-full-specifications-confirmed

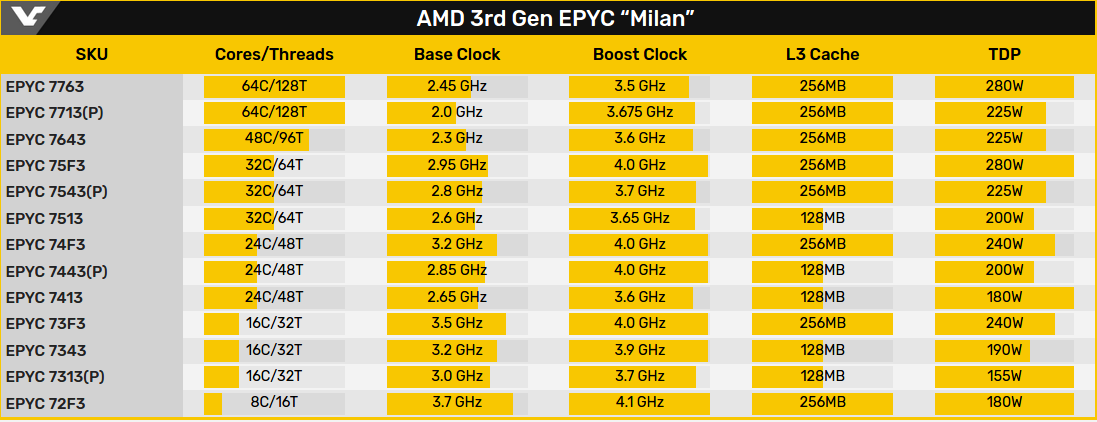

o que daria qualquer coisa como isto

https://videocardz.com/newz/amd-3rd-gen-epyc-milan-full-specifications-confirmed