You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Processador AMD ZEN4 (Ryzen 7000 series)

- Autor do tópico Nemesis11

- Data Início

Porque as correntes de fuga começam a ser enormes e crescem exponencialmente.Como é que se faz um shrink de 7nm para 5nm, mantendo o nº de cores e o TDP passa de 105w para 170w?

Juntamente com aumento nos gpu's, daqui a pouco estamos a usar fontes de 1500 watts e a gastar o dobro na fatura de energia.

muddymind

1st Folding then Sex

Simplesmente basta sair da zona de eficiência para puxar os clocks ao extremo mesmo que os ganhos sejam diminutos.

Vejam por exemplo o 12900k que mesmo após limitar imenso o tdp abaixo de 200w continua com quase a mesma performance

E recentemente o igor's lab limitou uma 3090 ti a 300w e perdeu apenas 10% da performance quando GPU bound com uma redução de 35% de consumo

Vejam por exemplo o 12900k que mesmo após limitar imenso o tdp abaixo de 200w continua com quase a mesma performance

E recentemente o igor's lab limitou uma 3090 ti a 300w e perdeu apenas 10% da performance quando GPU bound com uma redução de 35% de consumo

Roberto1973

Power Member

Primeiro geração CPU vão até 120w e depois versão com 3d-cache + Cores e muito mais....

Das RDNA 3 diz-se ser chiplet e que possivelmente a Navi 31 terá stacked cache

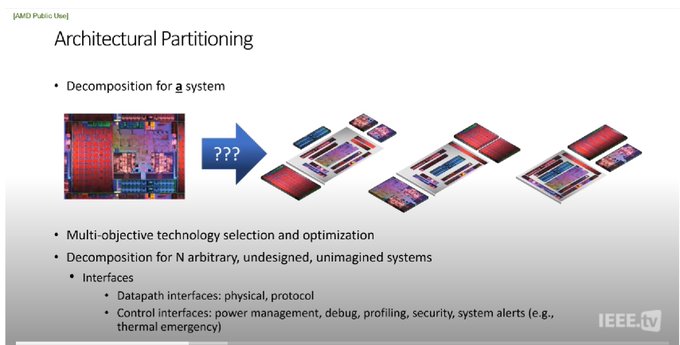

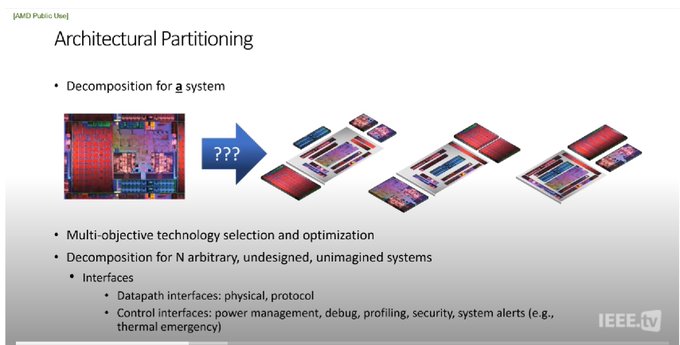

O MCD será a parte do "Memory Chiplet Die", e pela discussão acerca desse post, aparece isto relativamente ao que parece ser um "rearranjo" do die de um APU

que é retirado desta apresentação

O MCD será a parte do "Memory Chiplet Die", e pela discussão acerca desse post, aparece isto relativamente ao que parece ser um "rearranjo" do die de um APU

que é retirado desta apresentação

HIR Chiplet Workshop: Architectures and Business Aspects for Heterogeneous Integration

https://ieeetv.ieee.org/video/hir-c...usiness-aspects-for-heterogeneous-integrationNemesis11

Power Member

Nemesis11

Power Member

AMD's AM5 Launches With Only DDR5 Support for Ryzen 7000, Dual-Chipset Design

All signs indicate that AMD's next-gen AM5 socket platforms that will house the 5nm Ryzen 7000 'Raphael' processors will only support DDR5 memory when they arrive later this year, but it isn't official. However, we have now confirmed through multiple sources in the supply chain that the X670 and B650 AM5 platforms support only DDR5 memory, which has pricing implications for platforms built around AMD's upcoming Zen 4 processors. Additionally, we've also confirmed that AMD has moved to a chiplet-based design for the chipsets for its AM5 motherboards, so some models will come with two chipset dies.

Our sources tell us that the X670 and B650 motherboards have no provisions for DDR4 support, and it isn't yet clear if Ryzen 7000's memory controllers even support DDR4. If they do support DDR4, AMD could have plans for lower-tier A-Series motherboards with DDR4 support, but we're told that doesn't seem likely.

https://www.tomshardware.com/news/a...es-with-ddr5-support-only-dual-chipset-designLast week a report emerged suggesting that AMD will use a dual-chiplet design for AM5 platforms. ASMedia, AMD's long-term chipset partner, will provide the chips (fabbed on TSMC 6nm). We confirmed that the dual-chipset design applies only to the X670 platform, while B650 motherboards (and presumably A-series) will come with only one chip.

AMD's mainstream B650 platform will come with a single chipset chip that connects to the Ryzen 7000 CPU via a PCIe 4.0 x4 connection, though documents we've seen say that a PCIe 5.0 connection is available on some AM5 processors. This single chip provides eight lanes of PCIe 4.0 (four lanes for M.2 storage), four SATA ports, and a number of USB ports.

Meanwhile, the enthusiast X670 platform employs two of these chips (our sources confirm the chips are identical, not a north/southbridge-type arrangement), effectively doubling these connectivity options. This stands in contrast to AMD's approach with the current 500-series motherboards, which use different chips for the X- and B-series motherboards. The new approach will obviously provide cost and design flexibility advantages.

Alegadamente, AM5 só irá suportar DDR5, pelo menos nos chipsets "X670" e "B650".

Estes 2 chipsets, "X670" e "B650", vão usar o mesmo chip, criado pela ASMedia e fabricado a 6nm TSMC. A dferença é que as "X670" usam 2 destes chips e as "B650", só usam 1.

A "B650" liga-se ao CPU por 4 Links Pci-Ex Gen4 e tem mais 4 lanes Gen4, 4 portas SATA e portas USB. Parece que há a possibilidade de ligação com lanes Pci-Ex Gen5 entre o CPU e o Chipset, mas não dão detalhes se a "X670" duplica as ligações Gen4 ou se usa ligações Gen5, etc.

Miguel_Pereira

Power Member

Neste momento de transição para DDR5 era uma boa opção AM5 ainda permitir DDR4 (ao jeito do que a Intel fez) mesmo que nas board`s/chipset intermédios.

Tornava mais "fácil" o upgrade e talvez até atingir uma maior fatia de mercado.

Por outro lado deve tornar tudo mais simples e estável ser 100% DDR5. A actual plataforma com preços mais baixos serve para DDR4.

skandal

Power Member

- Quanta RAM quer colocar?

- SIM

https://www.tomshardware.com/news/a...es-with-ddr5-support-only-dual-chipset-design

Alegadamente, AM5 só irá suportar DDR5, pelo menos nos chipsets "X670" e "B650".

Estes 2 chipsets, "X670" e "B650", vão usar o mesmo chip, criado pela ASMedia e fabricado a 6nm TSMC. A dferença é que as "X670" usam 2 destes chips e as "B650", só usam 1.

A "B650" liga-se ao CPU por 4 Links Pci-Ex Gen4 e tem mais 4 lanes Gen4, 4 portas SATA e portas USB. Parece que há a possibilidade de ligação com lanes Pci-Ex Gen5 entre o CPU e o Chipset, mas não dão detalhes se a "X670" duplica as ligações Gen4 ou se usa ligações Gen5, etc.

Acho genial isso de "dual chipset", primeiro que evita custos de fazer um die maior e tal, abaixa o consumo e depois faz que a diferenciação entre ambos seja unicamente a quantidade de I/O. Só espero que não se corte features e tenha boards boas para ambos, pelo menos o B550 teve direito à boards top, ainda que as extreme foram todas X570.

Só não percebi se é 2 chips distintos separados ou um só, mas dual die.

Só tou achando o B650 com poucas lanes downstream, apenas 4 enquanto o B550 tem 6. Se bem que penso que o CPU tem 8 lanes para nvme o que para montar um sistema básico/microATX/ITX é mais que E suficiente. Num ITX daria para ter dual nvme + bt/wifi, lan e ainda ficaria 2 lanes por usar, ou seja na prática tem-se mais 2 lanes que AM4 com B550.

E assim o X670 fica para quem precisa realmente de imenso I/O

É possível que o "X670" conecte-se por pci 5.0, assim cada chip usa 2 lanes e tendo o mesmo bw upstream que 4x @ 4.0. Outro cenário é um daisy chain, o primeiro liga-se ao cpu via pcie 5 4x, expande as lanes da plataforma (tipo mais 8 lanes) e o segundo liga ao primeiro por pcie 4.0 4x e tem as 4 lanes downstream + SATA + USB. Teria assim 16 lanes por die, sendo 8 poderiam também ser SATA ou USB como ja ocorre com o IO die dos AM4 atuais.

Nemesis11

Power Member

A estratégia da AMD, desde o lançamento dos Ryzen, que passa por ter o mínimo de dies possíveis, para o máximo de produtos possíveis.Acho genial isso de "dual chipset", primeiro que evita custos de fazer um die maior e tal, abaixa o consumo e depois faz que a diferenciação entre ambos seja unicamente a quantidade de I/O. Só espero que não se corte features e tenha boards boas para ambos, pelo menos o B550 teve direito à boards top, ainda que as extreme foram todas X570.

Parece que iremos ver a mesma estratégia nos Chipsets e provavelmente, iremos ver a mesma estratégia em GPUs.

Será? Se a X670 ocupar mais lanes Pci-Ex do CPU, pode-se ter o cenário em que o ideal para I/O é a B650, porque, consoante os dispositivos que se queiram ligar, poderão estar ligados ao CPU, em vez de algum deles ter que ficar ligado ao Chipset.E assim o X670 fica para quem precisa realmente de imenso I/O

Vejo várias hipóteses para a ligação entre o CPU e a X670, com duas dies:É possível que o "X670" conecte-se por pci 5.0, assim cada chip usa 2 lanes e tendo o mesmo bw upstream que 4x @ 4.0. Outro cenário é um daisy chain, o primeiro liga-se ao cpu via pcie 5 4x, expande as lanes da plataforma (tipo mais 8 lanes) e o segundo liga ao primeiro por pcie 4.0 4x e tem as 4 lanes downstream + SATA + USB. Teria assim 16 lanes por die, sendo 8 poderiam também ser SATA ou USB como ja ocorre com o IO die dos AM4 atuais.

- Usar 4 lanes Pci-Ex Gen5 em vez de Gen4 na B650.

- Usar as mesmas 4 lanes Pci-Ex Gen4 e ter um Switch Pci-Ex à frente das 2 dies.

- Cada uma das dies ligar ao CPU por 2 lanes Pci-Ex independentes.

- Cada uma das dies ligar ao CPU por 4 lanes Pci-Ex independentes.

- Uma das dies não ligar directamente ao CPU e fazer a ligação pela outra die, como uma "proxy".

- Outra solução que me esteja a escapar.

Será interessante ver como é que a AMD irá ligar o cpu a 2 chipsets, sendo que neste caso, não há uma northbridge e uma southbridge.

Rolou uma imagem com ligação entre as duas dies 4 lanes pcie, portanto um "northbridge e southbridge", mas com 2 dies identicas e no mesmo package.

Também vi um tweet que dizia que é tudo PCIE 4.0 4x upstream, ou seja bottleneck. Se bem que hoje o X570 é pcie 4.0 4x upstream e tem 12-16 lanes + satas + usbs pendurados. E não esquecer que o AM5 tem mais 4 lanes e permite assim ligar 2 NVME direto no CPU.

Também vi um tweet que dizia que é tudo PCIE 4.0 4x upstream, ou seja bottleneck. Se bem que hoje o X570 é pcie 4.0 4x upstream e tem 12-16 lanes + satas + usbs pendurados. E não esquecer que o AM5 tem mais 4 lanes e permite assim ligar 2 NVME direto no CPU.

strafejump

Power Member

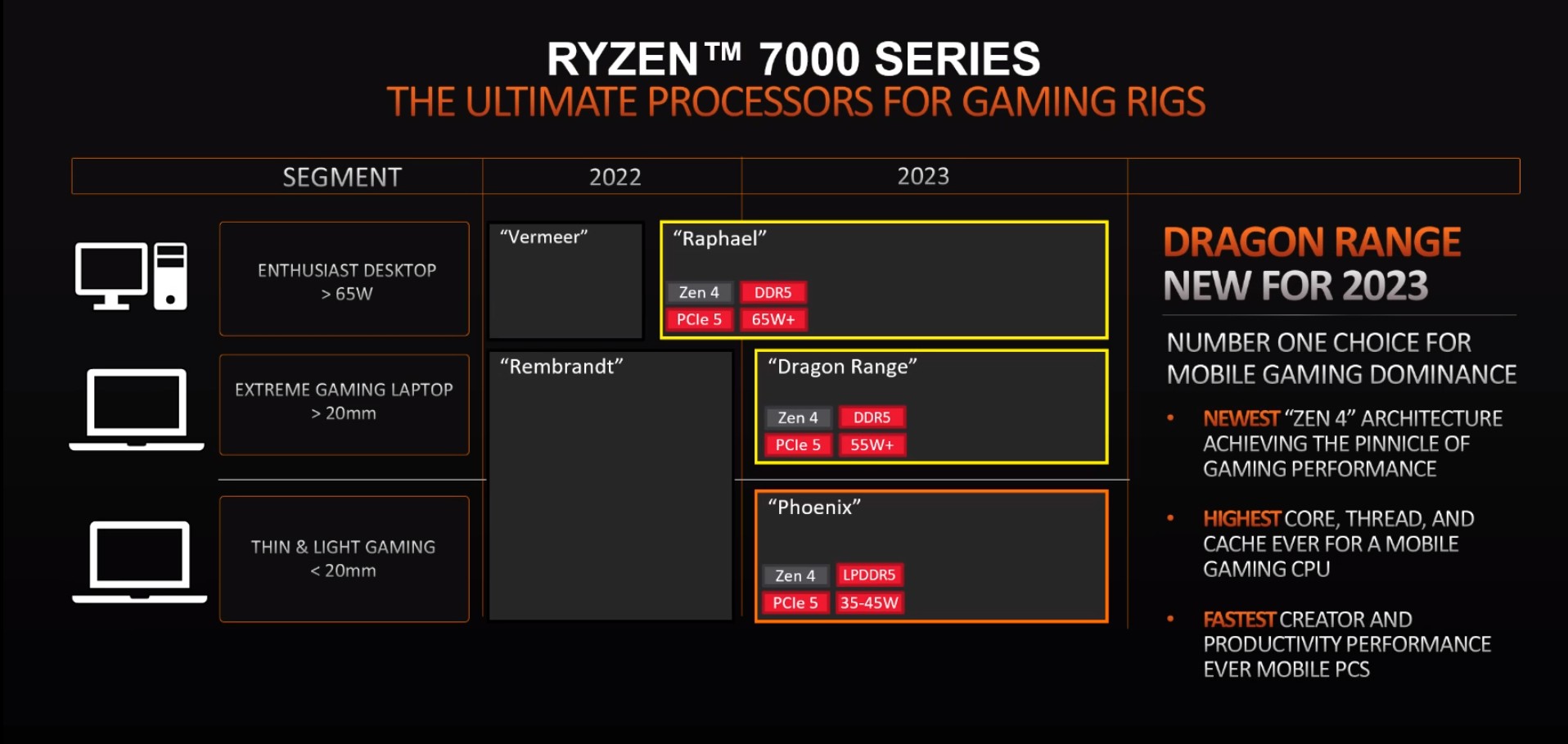

"highest core, thread and cache ever for a mobile gaming cpu"

isto quer dizer o quê? que vão usar os chiplets dos cpus desktop com os 32MB de cache em portáteis, ou que vão aumentar a cache nos apus monolíticos? seja de que maneira for, estes phoenix e dragon range vão fazer o funeral aos gpus de baixa gama.