muddymind

1st Folding then Sex

Há imensos tópicos espalhados com notícias de cores ARM sem grande arrumação por isso resolvi criar uma thread dedicada aos cores de referência da arm para começar a agregar todas as notícias num único local.

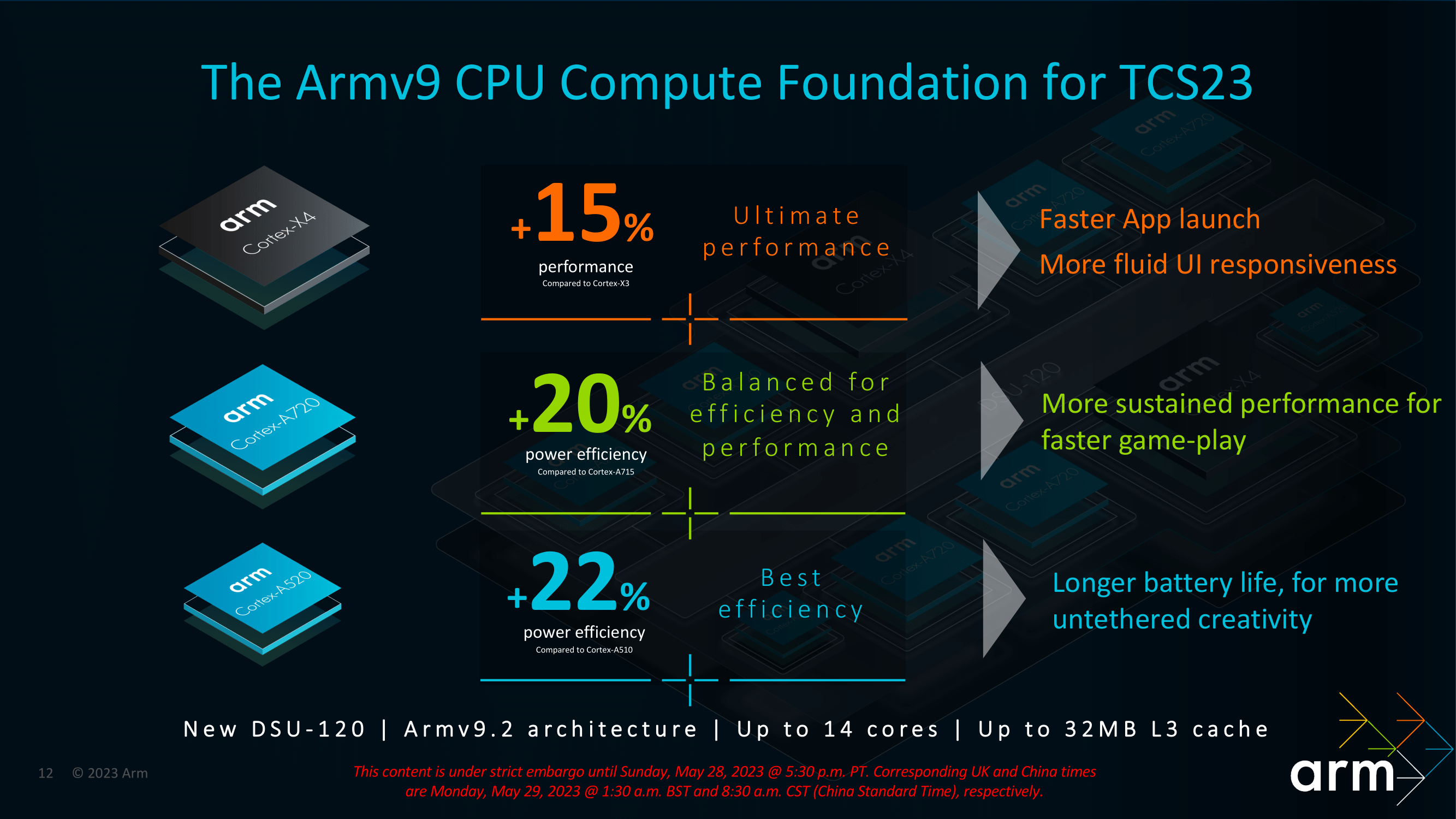

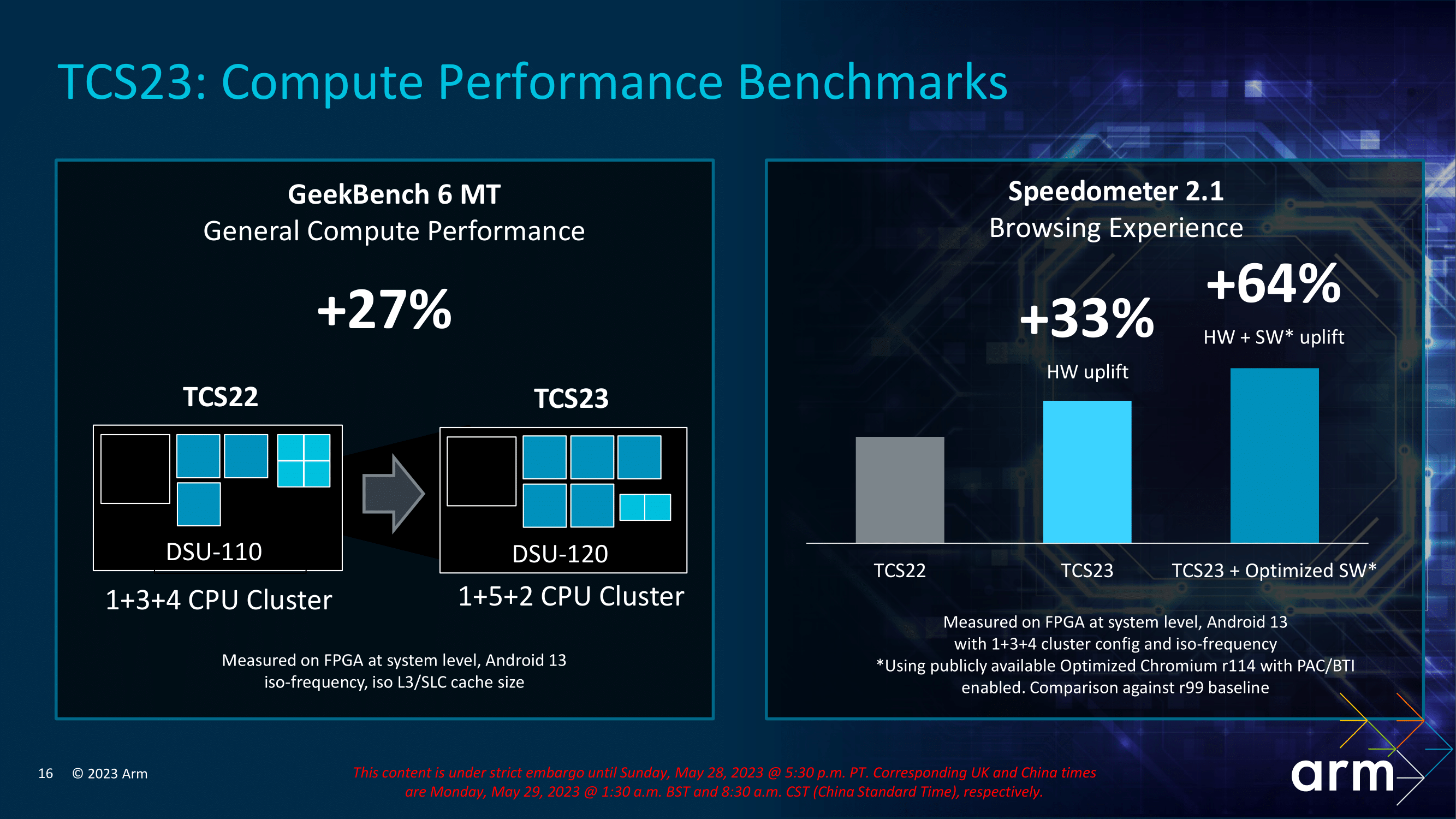

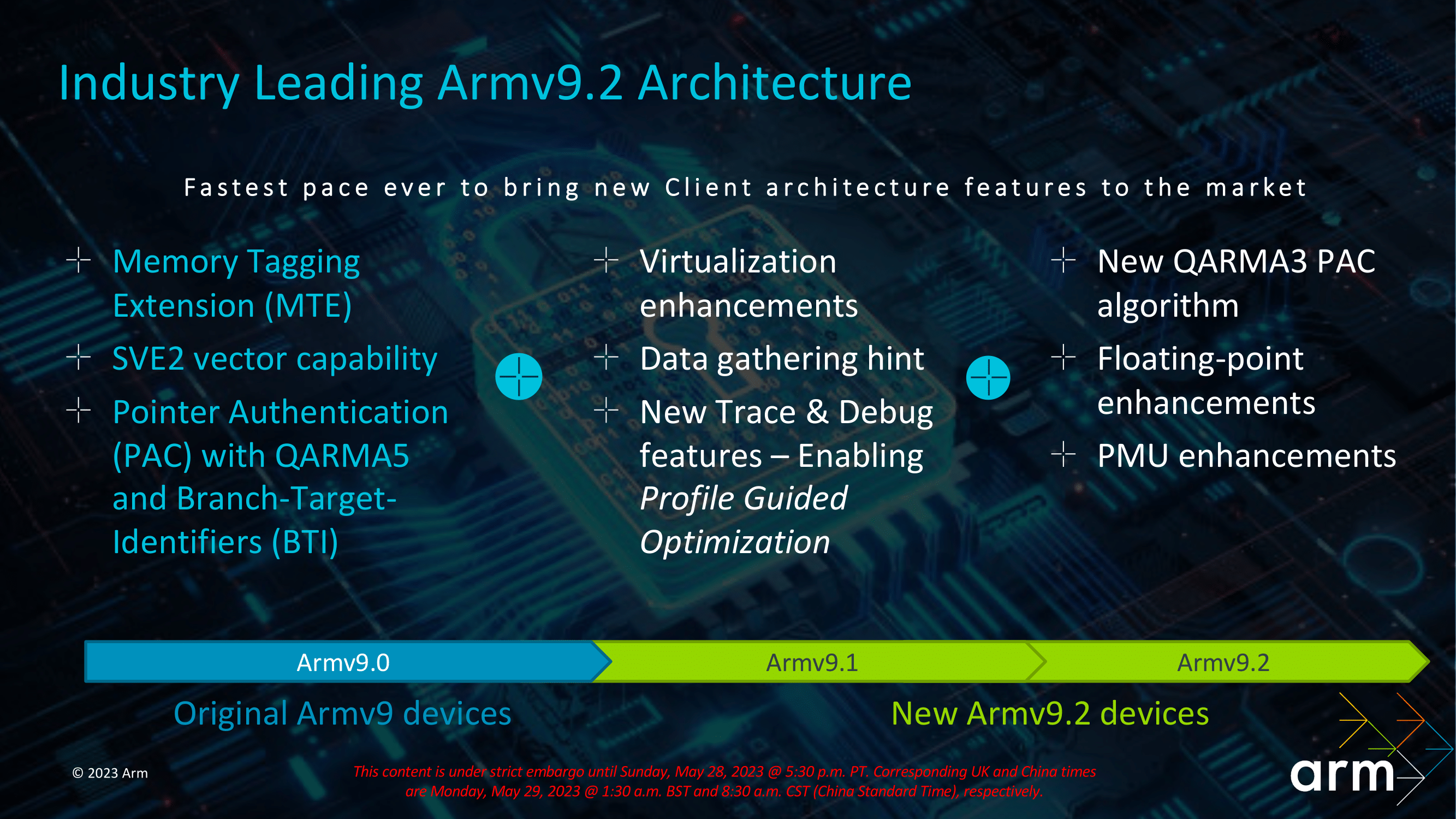

Arm Unveils Next-Gen Flagship Core: Cortex-X3

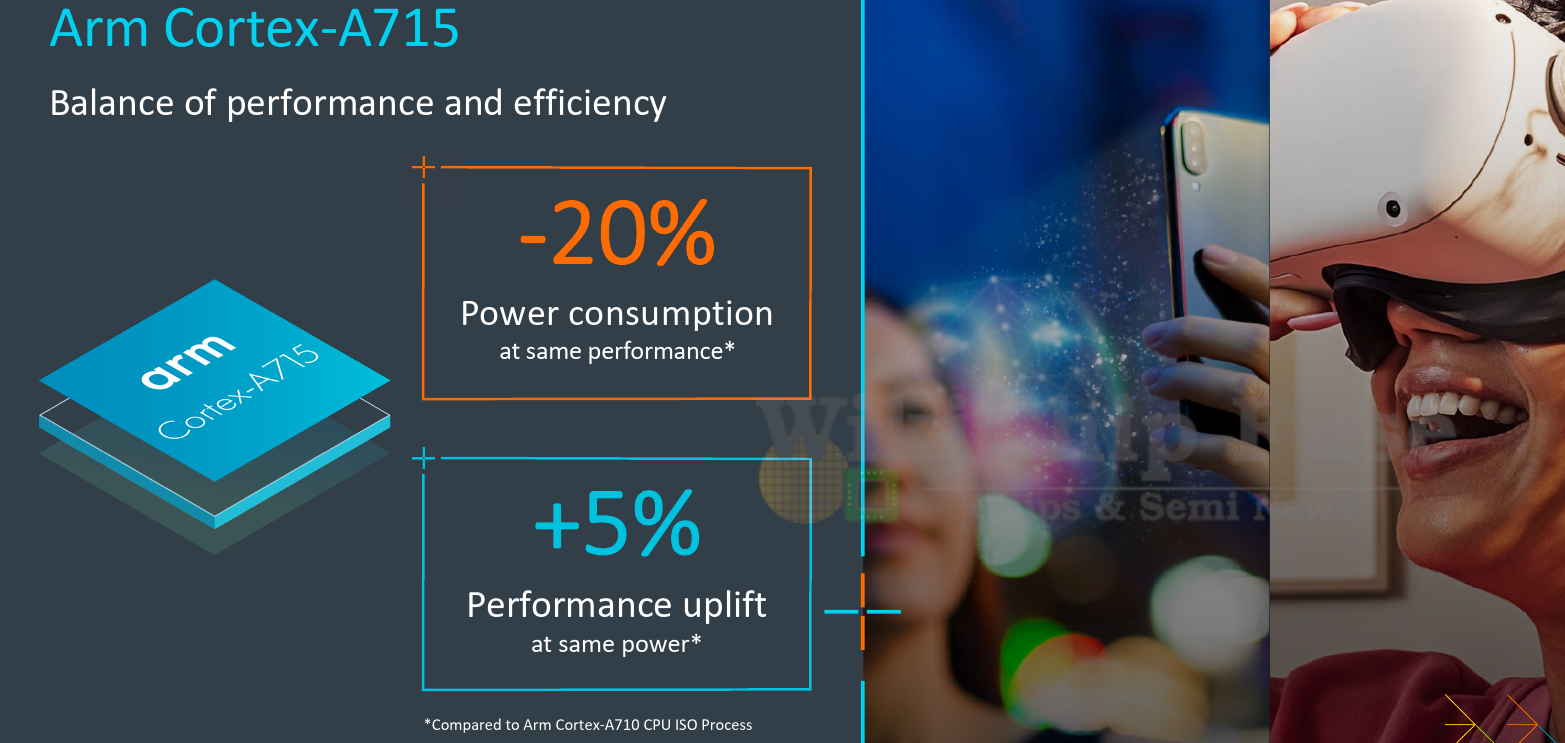

Arm Introduces The Cortex-A715

Arm Refreshes The Cortex-A510, Squeezes Higher Efficiency

A maior mudança foi a eliminação de suporte para aplicações 32-bit. Honestamente desilude não ver uma evolução maior sendo o pior caso o A510 que consome demasiado para a performance que oferece. A ARM tem mesmo que colocar o pé no acelerador que assim nunca irá competir no topo.

Arm Unveils Next-Gen Flagship Core: Cortex-X3

Arm Introduces The Cortex-A715

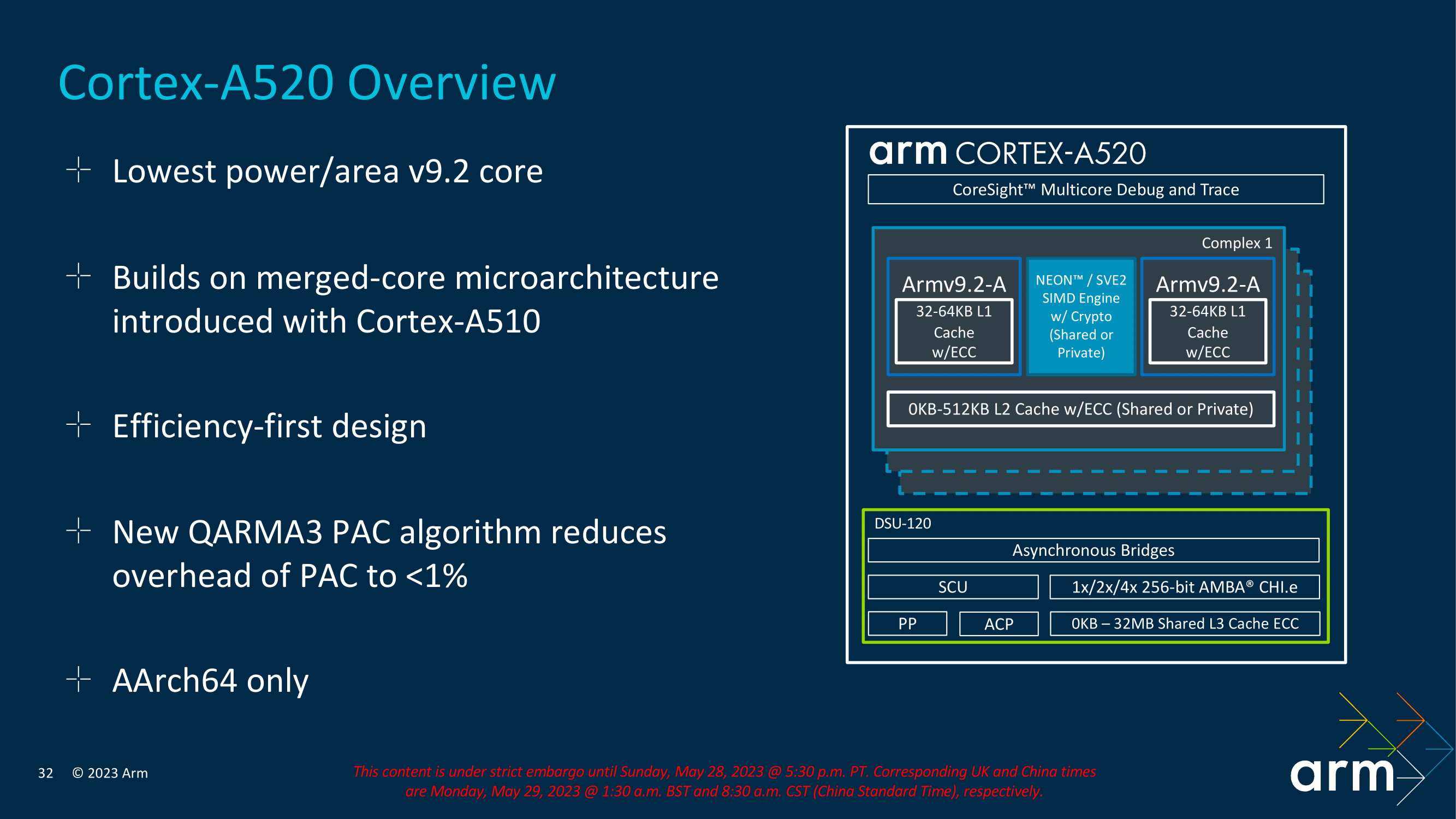

Arm Refreshes The Cortex-A510, Squeezes Higher Efficiency

A maior mudança foi a eliminação de suporte para aplicações 32-bit. Honestamente desilude não ver uma evolução maior sendo o pior caso o A510 que consome demasiado para a performance que oferece. A ARM tem mesmo que colocar o pé no acelerador que assim nunca irá competir no topo.