Isso n é só para a plataforma mobile? Vai haver CSI para ao notebooks?É, deve ser...

http://www.intel.com/technology/magazine/45nm/coremicroarchitecture-0507.htm

Para fazer isto é preciso ter PLL's separados que consigam gerir duas voltagens diferentes ao mesmo tempo, logo, split power planes.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Intel CSI explicado

- Autor do tópico blastarr

- Data Início

blastarr

Power Member

Isso n é só para a plataforma mobile? Vai haver CSI para ao notebooks?

Obviamente que sim, mas aqui nem estava a falar do bus CSI.

Estava a discutir a capacidade de cada core de uma CPU poder funcionar a uma voltagem (e logo, velocidade) diferente da dos outros.

As actuais tecnologias EIST e Cool'n'Quiet reduzem a velocidade e voltagem de toda a CPU, não possuem granularidade suficiente para decidir a velocidade de cada core individual em função da sua carga relativa num dado ciclo de relógio.

Esta capacidade aparecerá dentro de pouco tempo no mercado com os "Penryn" (Core 2 de 45nm) e com os "Barcelona" (K10, 65nm), não é preciso esperar pelos "Nehalem".

Zar0n

Power Member

Esta capacidade aparecerá dentro de pouco tempo no mercado com os "Penryn" (Core 2 de 45nm) e com os "Barcelona" (K10, 65nm), não é preciso esperar pelos "Nehalem".

Nop, no Barcelona só varia a frequência a voltagem é igual para todos os cores.

blastarr

Power Member

Nop, no Barcelona só varia a frequência a voltagem é igual para todos os cores.

É uma limitação dos chipsets com socket AM2/AM2+, não uma limitação da CPU em si.

Aliás, a capacidade sempre esteve prevista para as CPU's com socket AM3, lá para fins de 2008.

Zar0n

Power Member

É uma limitação dos chipsets com socket AM2/AM2+, não uma limitação da CPU em si.

Aliás, a capacidade sempre esteve prevista para as CPU's com socket AM3, lá para fins de 2008.

Estas a confundir as coisas, a voltagem é a mesma para todos os cores, só varia entre os cores e o controlador de memoria.

blastarr

Power Member

Estas a confundir as coisas, a voltagem é a mesma para todos os cores, só varia entre os cores e o controlador de memoria.

O "Penryn" varia a voltagem e não tem controlador de memória.

Os actuais "Barcelona" AM2+ não suportam o "decoupling" de cada core individual, mas suportarão essa capacidade nas variantes socket AM3.

Percebeste agora ?

Fazer a separação do clock generator do controlador de memória integrado sempre foi a prioridade e principal razão de existir do socket AM2+, não o suporte ao HyperTransport 3.0 (que interessa mais nos Opteron LGA 1207, os quais possuem 3 links HTT separados).

Um controlador de memória acima dos 3.0GHz é demasiado instável e cria problemas de flexibilidade para diversificar a gama e escalar a velocidade de relógio do master clock.

Além de que o HyperTransport 2.0 actual está longe de ficar saturado em sistemas single-socket como é o caso do 939/AM2/AM2+.

É uma das desvantagens de ter um controlador on-die.

Zar0n

Power Member

O "Penryn" varia a voltagem e não tem controlador de memória.

Os actuais "Barcelona" AM2+ não suportam o "decoupling" de cada core individual, mas suportarão essa capacidade nas variantes socket AM3.

Percebeste agora ?

Es teimoso, isso de AM3 já n é um barcelona, já k este nem funciona em AM3 e implica uma nova revisão do core.

blastarr

Power Member

Es teimoso, isso de AM3 já n é um barcelona, já k este nem funciona em AM3 e implica uma nova revisão do core.

Tu é que estás a ser teimoso.

O Phenom FX é um "Barcelona" com 2 dos 3 links HTT removidos e instalado num package para socket AM2/AM2+.

DJ_PAPA

Power Member

Socket AM2+:O "Penryn" varia a voltagem e não tem controlador de memória.

Os actuais "Barcelona" AM2+ não suportam o "decoupling" de cada core individual, mas suportarão essa capacidade nas variantes socket AM3.

Percebeste agora ?

http://www.xbitlabs.com/articles/cpu/display/amd-k10_10.html#sect2

E o socket AM3 nao é Barcelona, nem phenom. É sim o Shangai 8 core que serão 2 phenon X4 colados.

Zar0n

Power Member

Tu é que estás a ser teimoso.

O Phenom FX é um "Barcelona" com 2 dos 3 links HTT removidos e instalado num package para socket AM2/AM2+.

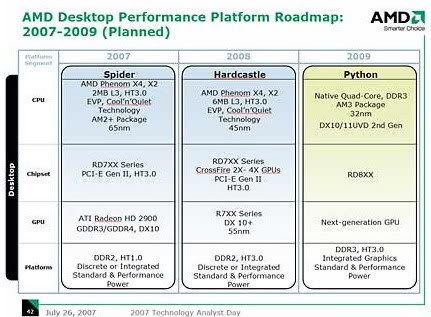

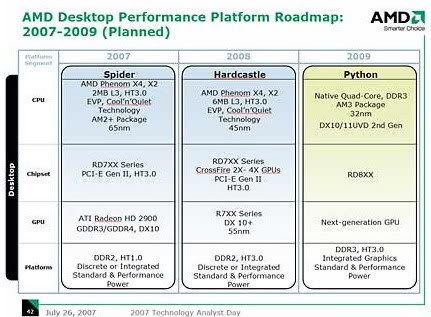

Pela ultima vez DDR3 é com a plataforma Python, n é barcelona.

blastarr

Power Member

Pela ultima vez DDR3 é com a plataforma Python, n é barcelona.

Mas qual plataforma ?

Estamos a falar da arquitectura K10, que correntemente é designada de "Barcelona" (da mesma maneira que "Conroe" e "Nehalem" designam grandes alterações na arquictura, apesar de tecnicamente dizerem respeito a apenas um dos vários modelos da família).

O core "Shanghai" é a mesma arquitectura, mas encolhida para 45nm e a usar o socket AM3 com suporte DDR3, nada mais.

Está para o "Barcelona" como o "Brisbane" estava para os "Windsor".

Última edição:

Zar0n

Power Member

Mas qual plataforma ?

Axo k é necessário um desenho, ou neste caso uma pic

DJ_PAPA

Power Member

O core "Shanghai" é a mesma arquitectura, mas encolhida para 45nm e a usar o socket AM3 com suporte DDR3, nada mais.

Está para o "Barcelona" como o "Brisbane" estava para os "Windsor".

Vai ter mais diferenças, nomeadamente alguns melhoramentos arquitecturais. Um pouco a semelhança do que vai acontecer com os C2D 65nm -> Penryn 45nm.

blastarr

Power Member

Axo k é necessário um desenho, ou neste caso uma pic

Pois, parece que não queres aprender.

Estamos a falar de CPU's e da sua arquitectura, tu vens com um gráfico que dá nomes de código do conjunto Motherboard + CPU + gráficos, e aliás nem diz nada acerca de uma nova arquitectura, como esperado.

Santa paciência...

Última edição:

Zar0n

Power Member

Pois, parece que não queres aprender.

Estamos a falar de CPU's e da sua arquitectura, tu vens com um gráfico que dá nomes de código do conjunto Motherboard + CPU + gráficos, e aliás nem diz nada acerca de uma nova arquitectura, como esperado.

Santa paciência...

Por isso é k disse plataforma.

Para fechar o assunto tu disseste:

"É uma limitação dos chipsets com socket AM2/AM2+, não uma limitação da CPU em si."

A limitação está no cpu.

Uma nova revisão do cpu pode mudar isso mas por agora a voltagem é igual em td os cores.

The end.