Sim, é possível que tenha a haver com o node/processo em si, e nesse caso se o seguinte estiver com melhores yields, é melhor cortar o mal pela raiz do que arrastar o problema.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Processador Intel Meteor Lake [2023]

- Autor do tópico muddymind

- Data Início

Roberto1973

Power Member

Intel meteor lake anulado.

Nemesis11

Power Member

O Meteor Lake, que agora deve ser só para portáteis, irá ter uma cache L4 e, ao contrário de gerações anteriores, penso que não usará eDRAM e sim SRAM e que será uma cache "tradicional". Em testes, estão a usar entre 128 e 512 MB. O nome é ADM/L4 e pode ser acedida pelo CPU e GPU.

Além disso, a L3 passará a ser só acedida pelo CPU.

Parece-me um projecto mais ambicioso que o 3DVcache da AMD, porque:

Além disso, a L3 passará a ser só acedida pelo CPU.

https://www-coelacanth--dream-com.t...=ja&_x_tr_tl=en&_x_tr_hl=en-US&_x_tr_pto=wappIntel's Fei Yang revealed that Meteor Lake GPUs do not support LLC (Last Level Cache) in a patch published on the intel-gfx mailing list , and newly support ADM/L4 cache.

The conventional Intel iGPU has a configuration in which the LLC can be shared by the CPU and GPU, and it was possible to allocate it to the cache on the GPU side according to the MOCS (Memory Object Control State) value.

With the Meteor Lake GPU , the LLC will be used only by the CPU and cannot be allocated to the GPU side cache.

It can be said that it is close to the cache configuration of Intel dGPU and AMD APU in that it does not have a cache that can be shared by CPU and GPU.

As an aside, a while ago there was a story that the built-in GPU performance of the Ryzen 9 7950X3D is four times that of the 7950X (actually a misunderstanding due to the reviewer's previous verification data) 1 , AMD APU cache configuration If I knew, I could have noticed the mistake.

And Meteor Lake GPUs will support L4 cache, also known as ADM.

The patch doesn't mention what ADM stands for or the size of the ADM/L4 cache.

In the Intel GPU driver, the sampler's cache is L2, and the cache shared by the entire GPU Device is L3.

There is a move to redefine the cache hierarchy in the X e -Core architecture , where the traditional GPU L3 cache was called the L2 cache, but recently published documents called it his Device Cache. 2It

may have been inconvenient in terms of consistency with drivers and past documents.

Speaking of L4 cache in Intel iGPU, eDRAM supported by Gen9 architecture is remembered.

However, while eDRAM was a memory side cache, a cache that can be used throughout the SoC (also called SLC, System Level Cache), the ADM/L4 cache is a cache that can be allocated on the GPU side.

The ADM/L4 cache is probably a cache that has changed the role of the conventional LLC rather than a memory side cache. Also, it seems that it can be used from the CPU instead of the GPU-only cache.

In that case, the conventional cache configuration will be inherited after all.

However, since the device information of the Meteor Lake GPUhas_llc=0 is set, LLC cannot be used even if there is no ADM/L4 cache, in which case it will be close to Intel dGPU and AMD APU.

What is worrisome is where the ADM/L4 cache is installed in Meteor Lake , but it is probably the Base Tile.

Intel has released a tile configuration for Meteor Lake , which stacks his GPU, SoC, CPU and IO Extender Tile on the Base Tile. Equipped with ADM/L4 cache, he doesn't appear to be configured to add Tile as an option.

There is also the possibility of SoC Tile with a memory controller, but there is no cache in the internal block of SoC Tile announced at HotChips34.

Intel has already put part of the cache on the Base Tile with Ponte Vecchio . Ponte Vecchio 's L3 cache is a combination of his L3 cache in the Base Tile and his RAMBO cache stacked on top of the Base Tile.

So at the moment we think it's the Base Tile that will likely feature his ADM/L4 cache in Meteor Lake .

Assuming that it is in the Base Tile, the difference in ADM/L4 cache size gives whether the Base Tile is common across Meteor Lake SKUs, or whether the ADM/L4 cache size is also adjusted according to the size of the GPU and CPU Tile. There are various points to worry about, such as the impact on GPU and CPU performance.

Parece-me um projecto mais ambicioso que o 3DVcache da AMD, porque:

- Dimensões maiores.

- Cache separada e um nível abaixo da L3.

- Terá consequêcias na performance do iGPU (Os Zen4 actuais têm iGPU, mas é demasiado pequeno).

- Provavelmente não terá acessos assimétricos entre os diversos cores do CPU.

Última edição:

O Meteor Lake, que agora deve ser só para portáteis, irá ter uma cache L4 e, ao contrário de gerações anteriores, penso que não usará eDRAM e sim SRAM e que será uma cache "tradicional". Em testes, estão a usar entre 128 e 512 MB. O nome é ADM/L4 e pode ser acedida pelo CPU e GPU.

Além disso, a L3 passará a ser só acedida pelo CPU.

https://www-coelacanth--dream-com.t...=ja&_x_tr_tl=en&_x_tr_hl=en-US&_x_tr_pto=wapp

Parece-me um projecto mais ambicioso que o 3DVcache da AMD, porque:

- Dimensões maiores.

- Cache separada e um nível abaixo da L3.

- Terá consequêcias na performance do iGPU (Os Zen4 actuais têm iGPU, mas é demasiado pequeno).

- Provavelmente não terá acessos assimétricos entre os diversos cores do CPU.

Não acredito que traga grandes vantagens no desktop com DDR5 7000+mhz. Com as boards e imcs next gen deve ser relativamente fácil e barato ter ddr5 8000mhz.

Se ainda fosse L3 maior... Podiam fazer um chip gaming com um tile de L3 em vez de igpu.

Roberto1973

Power Member

Cache L4 só para cpu nada igpu.

Nemesis11

Power Member

Acho que estás enganado. A latência e bandwidth de SRAM comparado com DRAM é muito considerável. A nível do CPU há duas vantagens. O CPU passa a ter acesso exclusivo à cache L3 e se a cache L4 não estiver a ser usada pelo iGPU, passa a ter mais um nível de cache, bem maior, para seu uso.Não acredito que traga grandes vantagens no desktop com DDR5 7000+mhz. Com as boards e imcs next gen deve ser relativamente fácil e barato ter ddr5 8000mhz.

Qualquer programa que caiba em Cache e não tenha grandes acessos a DRAM, vai ter aumentos de performance consideráveis.

Dito isto, este Meteor lake parece ser só para o mercado mobile, por isso não será visível as vantagens em Desktops. Ver que vantagens há em Desktops, depende se o Arrow Lake terá ou não esta Cache L4.

A cache L3, na prática, passa a ser maior, porque será de uso exclusivo do CPU. Isto fora o tamanho e uso da L4.Se ainda fosse L3 maior... Podiam fazer um chip gaming com um tile de L3 em vez de igpu.

Features de segurança na L4? Que features de segurança precisam de uma L4?Ao ler o que está, a L4 nem esta lá para performance, mas features de segurança, IA e afins, relembrar que sendo chips mobile e com isso algo que o mercado empresarial precisa.

A cache L4 está ali só por questões de performance, seja CPU, iGPU, IA, etc.

Não é o que as noticias indicam. A L4 passa a ser a LLC, para acessos do CPU e iGPU. A L3 é que passa a ser de uso exclusivo do CPU.Cache L4 só para cpu nada igpu.

Roberto1973

Power Member

Nemesis11@

The description from the Linux patch reads: "On MTL, GT can no longer allocate on LLC - only the CPU can. This, along with addition of support for ADM/L4 cache calls a MOCS/PAT table update."

The description from the Linux patch reads: "On MTL, GT can no longer allocate on LLC - only the CPU can. This, along with addition of support for ADM/L4 cache calls a MOCS/PAT table update."

Nemesis11

Power Member

A LLC referida nesse comentário, que está no código dos drivers dos GPU da Intel em Linux, refere-se à L3. Foi exactamente o que eu disse, a L3 deixa de ser acedida pelo CPU e GPU e passa a ser exclusiva do CPU e a ADM/L4 é que passa a ser usada pelo GPU.Nemesis11@

The description from the Linux patch reads: "On MTL, GT can no longer allocate on LLC - only the CPU can. This, along with addition of support for ADM/L4 cache calls a MOCS/PAT table update."

Alías, o código que está no patch indica isso mesmo.

+ if (IS_METEORLAKE(i915))

+ mtl_setup_private_ppat(uncore);

+static void mtl_setup_private_ppat(struct intel_uncore *uncore)

+{

+ intel_uncore_write(uncore, GEN12_PAT_INDEX(0),

+ MTL_PPAT_L4_0_WB);

+ intel_uncore_write(uncore, GEN12_PAT_INDEX(1),

+ MTL_PPAT_L4_1_WT);

+ intel_uncore_write(uncore, GEN12_PAT_INDEX(2),

+ MTL_PPAT_L4_3_UC);

+ intel_uncore_write(uncore, GEN12_PAT_INDEX(3),

+ MTL_PPAT_L4_0_WB | MTL_2_COH_1W);

+ intel_uncore_write(uncore, GEN12_PAT_INDEX(4),

https://lists.freedesktop.org/archives/intel-gfx/2023-April/323891.html/* (e)LLC caching options */

/*

@@ -73,6 +78,12 @@ struct drm_i915_mocs_table {

#define L3_2_RESERVED _L3_CACHEABILITY(2)

#define L3_3_WB _L3_CACHEABILITY(3)

+/* L4 caching options */

+#define L4_0_WB _L4_CACHEABILITY(0)

+#define L4_1_WT _L4_CACHEABILITY(1)

+#define L4_2_RESERVED _L4_CACHEABILITY(2)

+#define L4_3_UC _L4_CACHEABILITY(3)

Última edição:

Roberto1973

Power Member

L4 não é usada pelo gpu, mas sim pelo cores

Nemesis11

Power Member

On MTL, GT can no longer allocate on LLC - only the CPU can.

Código:

/* (e)LLC caching options */

/*

@@ -73,6 +78,12 @@ struct drm_i915_mocs_table {

#define L3_2_RESERVED _L3_CACHEABILITY(2)

#define L3_3_WB _L3_CACHEABILITY(3)Ok, para mim, isto tem zero lógica, mas se no final for assim que o Meteor Lake tem a sua hierarquia de caches, cá estarei para dizer que estava enganado.

Intel Core "Meteor Lake" Now Ramping for Production, Market Release in 2H-2023

https://www.techpowerup.com/307918/...ping-for-production-market-release-in-2h-2023

Deve estar a apontar para a Computex.

https://www.techpowerup.com/307918/...ping-for-production-market-release-in-2h-2023

Deve estar a apontar para a Computex.

Intel PR Confirms Chip Branding Changes in the Works: Core i Series to Give Way to Ultra?

https://www.anandtech.com/show/1884...es-in-the-works-i-series-to-give-way-to-ultra

Supostamos

"Confirma-se" o cancelamento da versão desktop.

"Confirma-se" o cancelamento da versão desktop.

:format(webp)/cdn.vox-cdn.com/uploads/chorus_asset/file/24729612/1.jpg)

:format(webp)/cdn.vox-cdn.com/uploads/chorus_asset/file/24729613/2.jpg)

Intel is officially killing off the ‘i’ in Core i7 — as it goes Ultra

https://www.theverge.com/21559670/intel-core-rebrandDiogoAntunes

Power Member

https://videocardz.com/newz/alleged...13700k-in-cpuz-cinebench-multi-threaded-tests

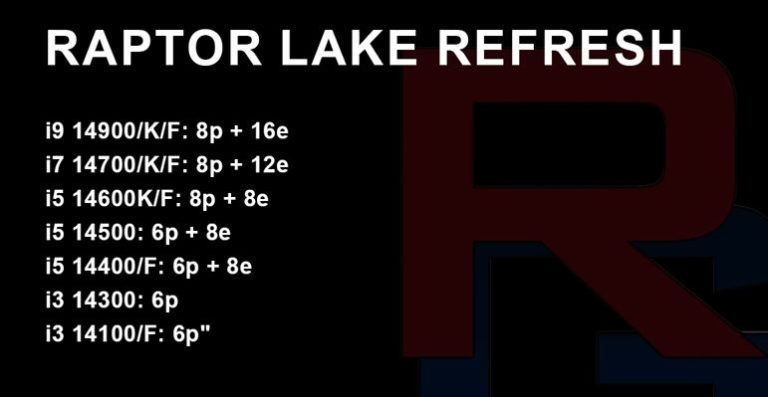

Ai temos o refresh, com + 4% Single Thread +100mhz performance , a confirmar/se e como fizeram com o Raptor Lake 11 gen, neste caso temos e mais E/Cores.

Cps

Ai temos o refresh, com + 4% Single Thread +100mhz performance , a confirmar/se e como fizeram com o Raptor Lake 11 gen, neste caso temos e mais E/Cores.

Cps

https://videocardz.com/newz/alleged...13700k-in-cpuz-cinebench-multi-threaded-tests

Ai temos o refresh, com + 4% Single Thread +100mhz performance , a confirmar/se e como fizeram com o Raptor Lake 11 gen, neste caso temos e mais E/Cores.

Cps

4% devem ser 200-300mhz a mais. Mas o mais importante é o DLVR, que vai melhorar eficiência. No entanto não deve fazer milagres, 10nm nunca vai ser tão eficiente como amd 5nm.

O clock no aida64 deve ser all-core. 13700k all core = 5.3ghz. 5.5ghz = 13900k o que faz todo o sentido, mas com DLVR não deve precisar de tanta voltagem.

É um bom upgrade para quem tem 12th gen. Useless para quem já tem um chip 13th gen decente.

Última edição: