Está relacionado com o meu post de dia 11 de Outubro, mas sendo uma posição da RISC-V Foundation, o caso já seria bem anterior.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Processador Risc-V

- Autor do tópico Dark Kaeser

- Data Início

Pois.

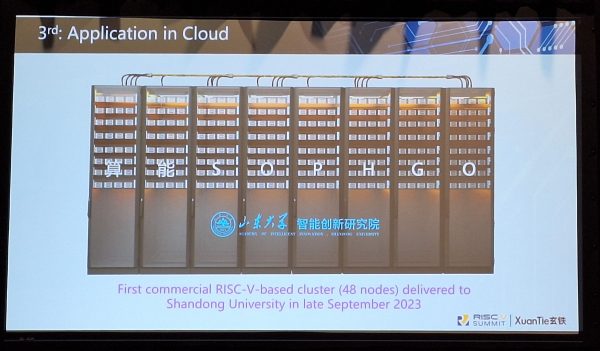

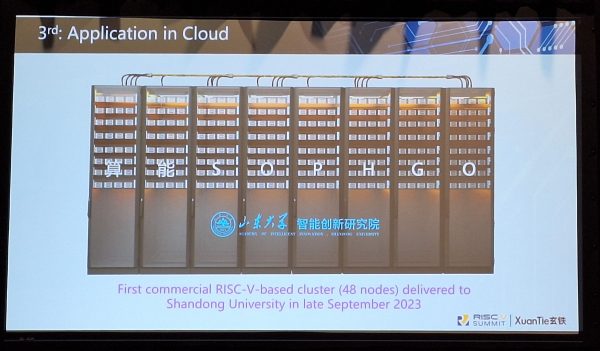

China Deploys Massive RISC-V Server in Commercial Cloud

Last month, China’s Shandong University deployed a server cluster with RISC-V CPUs. The system has a total of 3,072 cores, with 48 nodes of 64-bit RISC-V CPUs.

The system is for Shandong University’s teaching and research purposes but is also available for cloud computing instances, Chen said in response to a question from HPCwire for more details on the system. He added that the system was finished and delivered in September and October.

The RISC-V system delivered to Shandong University system uses Sophgo’s SG2042 chip, which has a clock speed of 2GHz and 64 M.B. of cache. The system supports the PCIe Gen 4 interface.

Sophgo released its RISC-V chip earlier this year, and ***** worked with the company to bring Linux O.S. to the chip. Software support for RISC-V is still weak despite growing adoption, and Chen called on developers globally to support 20,000 cloud computing packages to RISC-V.

China’s Plan for RISC-V

https://www.hpcwire.com/2023/11/08/china-deploys-massive-risc-v-server-in-commercial-cloud/The Chinese Academy of Sciences (CAS) is developing an advanced RISC-V chip called XiangShan-v3 in collaboration with top Chinese companies, including *****, Tencent, and ZTE. CAS hopes the chip will match the performance of ARM’s Neoverse-N2 server CPU design, which was announced in 2021.

@Nemesis11

Olha o mistério desvendado dias depois.

Olha o mistério desvendado dias depois.

Chinese Company Developing 64-core RISC-V Chip with Tech from U.S.

Sophgo is developing the SG2380 high-performance chip based on designs in the RISC-V community. The company also announced a new SG2044 chip that it plans to release next year.

The SG2380 has a 16-core SiFive P670 design and is connected to SiFive’s X280 accelerator. SiFive, based in the U.S., makes chips based on the RISC-V design.

The SG2380 was touted as a high-performance desktop chip by Liuxi Yang, chief scientist at Sophgo Technologies, during a presentation at SC 2023.

It also has an Imagination AXT-16-512 graphics processor, which supports gaming and machine-learning applications. The chip is being designed using A.I. and will ship next year.

The Chinese company Sophgo started as Sophon in 2016, developing bitcoin mining hardware. Sophgo was established in 2020 and was focused on developing A.I. chips. Sophon and SophGo merged in 2021 and shipped its first CPU, SG2042, in 2022.

The 64-core Sophgo SG2042 has seen some success. Shandong University deployed a RISC-V server with 48 chips last month, and it is open to academia and commercial cloud customers.

https://www.hpcwire.com/2023/11/13/...oping-64-core-risc-v-chip-with-tech-from-u-s/Sophgo is also developing a successor, the SG2044, which will ship in 2024. The upgraded chip has the final RISC-V vector extensions, which were recently ratified, while the SG2042 has the older version 0.7 vector extensions.

RISC-V extensions have compatibility issues, and the company had to develop a new chip to accommodate the final vector extensions, Liuxi told HPCwire.

Otherwise, the 64-core Sophgo 2044 is an incremental upgrade — it will support PCIe Gen5, Gigabit Ethernet, and LPDDR5x. It will draw up to 120 watts of power. Liuxi said the SG2380 and SG2044 chips will likely be manufactured using TSMC’s 12-nanometer process.

Sophgo came to SC23 hoping to drum up interest in its chips.

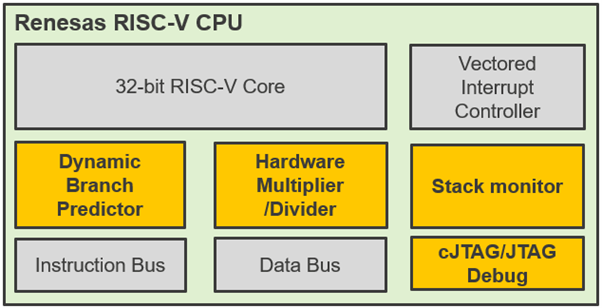

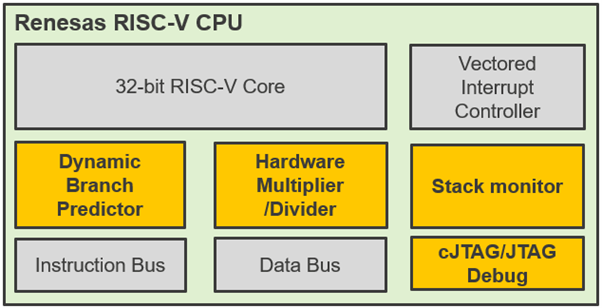

A Renesas acaba de anunciar o seu primeiro core risc-v 32bits, o que usavam actualmente era licenciado à Andes Technologies.

RISC-V to the Core: New Horizons

In the past, Renesas has embraced RISC-V technology introducing 32-bit ASSP devices for voice-control and motor-control built on CPU cores developed by Andes Technology Corp.

The exciting next step is the availability of the first, in-house engineered, CPU core. A high-level block diagram of the CPU is shown below:

https://www.renesas.com/us/en/blogs/risc-v-core-new-horizonsBut what‘s so special about it? First, this CPU is suitable for many different application contexts. It can be used as main CPU or to manage an on-chip subsystem or even to be embedded in a specialized ASSP device. Clearly it is very flexible. Second, the implementation is very efficient in terms of silicon area, which helps reduce operating current and leakage current during standby time, besides the obvious effect of smaller cost impact. Third, despite targeting small embedded systems, it provides a surprisingly high level of computational throughput to fulfill the increasingly demanding performance requirement of even deeply embedded applications.

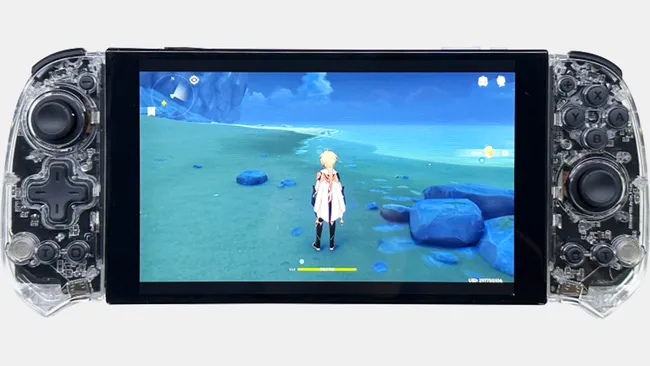

World's first RISC-V handheld gaming system announced — retro gaming platform uses Linux

Sipeed officially positions the Lichee Pocket 4A as a "RISC-V Debian+Android RetroGame platform." As the name suggests, it's designed to run simplistic retro games using GPU acceleration or even software rendering. The unit uses the LM4A system-on-module based on *****'s T-Head TH1520 RISC-V processor. It packs four RISC-V Xuantie C910 general-purpose cores running at 2.50 GHz and an unknown Imagination GPU.

The device can run Google's Android or Debian operating systems and should potentially support the majority of games for those OSes. Meanwhile, it's unclear how many true retro games (which were developed, say, for DOS) can run on these platforms.

https://www.tomshardware.com/pc-com...com&utm_medium=social&utm_campaign=socialflowThe Sipeed RetroGame platform can be equipped with a 7-inch 1280x800 LCD touchscreen, 8 or 16 GB of LPDDR4X memory, and 32GB or 128GB of eMMC storage. It also has Wi-Fi + Bluetooth 5.4 wireless connectivity and a plethora of wired connectors (USB 3.0, USB 3.0 Type-C, GbE, and a 3.5-mm headphone jack). The unit weighs 490 grams, which is significantly below the weight of Valve's Steam Deck, though much of the difference likely stems from the cooling and battery used on the Steam Deck.

É o mesmo chip da Lichee Console 4A

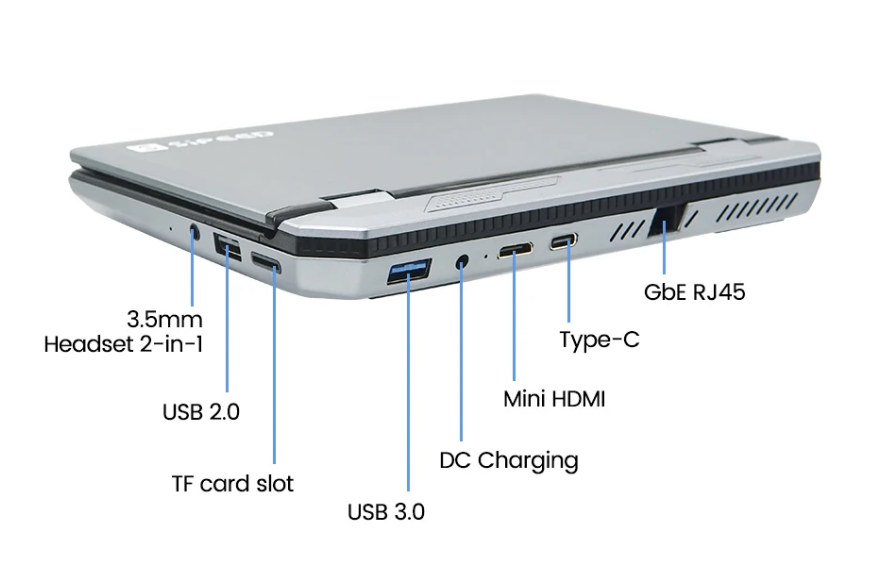

Lichee Console 4A RISC-V mini laptop sells for $252 and up

Sipeed Lichee Console 4A is a RISC-V portable Linux console, that I would also call a RISC-V mini laptop, powered by an ***** T-Head TH1520 quad-core C910 processor and equipped with up to 16GB RAM and 128GB eMMC flash.

Lichee Console 4A specifications:

- SoM – Replaceable Lichee LM4A system-on-module based on TH1520 quad-core RISC-V C910 processor with up to 16GB LPDDR4X, 128GB eMMC flash

- Storage – MicroSD card slot, M.2 SSD support

- Display – 7-inch 1280 x 800 LCD with capacitive touch

- Video Output – 1x mini HDMI

- User Input – Capacitive touch, 72-key keyboard with “RedPoint” pointing stick

- Camera – 2MP front-facing camera

- Audio

- 3.5mm headphone jack

- MEMS MIC + stereo speaker

- Networking

- Gigabit Ethernet RJ45 port

- WiFi 6 and Bluetooth 5.4

- USB – 1x USB 3.0 Type-A port, 1x USB 3.0 Type-C port, 1x USB 2.0 Type-A port

- Battery – 3,000 mAh @ 7.6V good for about 2 to 3 hours

- Power Supply – 12V DC via power barrel jack or 5V via USB-C port

- Power Consumption – Idle: 7~8W; under load: 11W

- Dimensions – 18 x 14 x 2 cm (Aluminum Alloy Case)

- Weight – 650 grams

Sipeed provides both Debian and Android 13 images for the portable computer which you can find on the wiki along with a few more technical details. We are told the RISC-V mini laptop can be used for programming with VSCode, hardware design with KiCad, office works with LibreOffice, and it’s also possible to watch 4K video and play some retro games. Bear in mind that while software support for the RISC-V architecture has progressed a lot in the last few years, there’s still more work to do to make it more mature. So it should probably be seen more as a development kit than a RISC-V consumer product.

https://www.cnx-software.com/2023/12/14/lichee-console-4a-risc-v-mini-laptop/So most people will probably pre-order a complete machine with one of the available configurations:

- $355 with 8GB RAM and 32GB eMMC flash

- $399 with 16GB RAM and 128GB eMMC flash

- $459 with 16GB RAM, 128GB eMMC flash, and 1TB SSD

Iria acontecer mais cedo ou mais tarde

Leading Semiconductor Industry Players Join Forces to Accelerate RISC-V

https://www.techpowerup.com/312056/...stry-players-join-forces-to-accelerate-risc-v

The RISC-V startup formed by major semiconductor companies Bosch, Infineon, Nordic, NXP and Qualcomm has been named Quintauris and has appointed Alexander Kocher as CEO.

Kocher took over as CEO in December 2023 having previously served as CEO of Elektrobit, a supplier of software products for the automotive industry. Prior to joining Elektrobit in 2011, Kocher was vice president and general manager of Wind River’s automotive business unit. Kocher has also held multiple senior management and engineering roles in Continental, Siemens and Infineon.

https://www.eenewseurope.com/en/european-risc-v-startup-is-named-quintauris-appoints-ceo/It appears that Quintauris is not being set up to develop RISC-V cores – but to encourage the adoption of compatible products based on the open-source RISC-V architecture. This will include the provision of reference architectures and help establish industry standards with an initial application focus on automotive but with an eventual expansion to include mobile and IoT.

E a publicação de um estudo interessante por parte dos chineses

With “Big Chip,” China Lays Out Aspirations For Waferscale

Researchers at the Institute of Computing Technology at the Chinese Academy of Sciences have just published a paper in a journal called Fundamental Research that talks about the limits of lithography and chiplets and proposes an architecture they call “Big Chip” that mimics the ill-fated waferscale efforts of Trilogy Systems back in the 1980s and the successful waferscale architecture of Cerebras Systems here in the 2020s.

The paper put together by the Chinese Academy of Sciences talks a lot about why one needs to develop waferscale devices, but it doesn’t provide much detail on what the Big Chip architecture they have developed actually looks like. And it does not indicate whether Big Chip will take the chiplet approach like Tesla did with Dojo or go all the way to waferscale like Cerebras did from the get-go. But the implication is clear that, just like Tesla, the Chinese government could fund such an effort if it wanted to.

According to the CAS researchers, the Big Chip implementation known as “Zhejiang,” which is Chinese for “crooked river and which is also the name of a mountainous, densely populated province in eastern China that has Hangzhou as it capital, will be done in a 22 nanometer process, presumably by Semiconductor Manufacturing International Corp (SMIC), the indigenous foundry in the Middle Kingdom that also has 14 nanometer processes ramped up and is working towards getting better yields with its 7 nanometer processes.

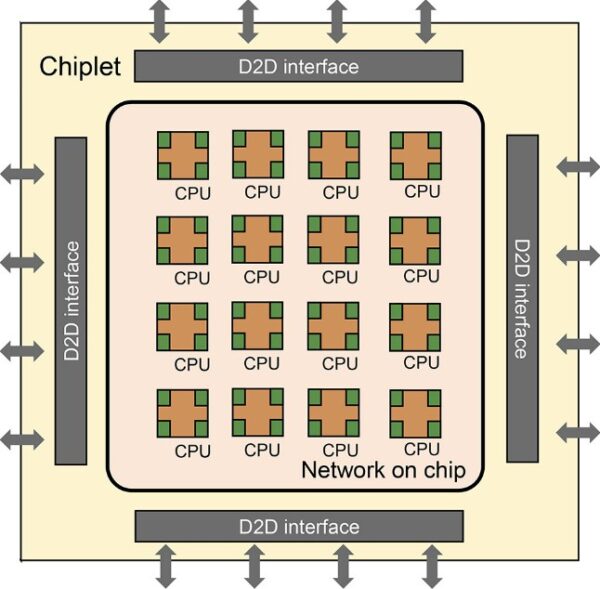

The Zhejiang Big Chip is comprised of 16 chiplets, each with 16 RISC-V cores. The researchers say that the design has the ability to scale up to 100 chiplets in a single discrete device, which we used to call a socket but that sounds more like a system board to us. It is not clear how those 100 chiplets would be configured or what kind of memory architecture would be implemented across those chiplets, which would have 1,600 cores in an array.

What we do know is that with the Zhejiang iteration of Big Chip there are 16 RISC-V processors connected to each other with symmetric multiprocessing across their shared main memory using a network on a chip, and there are SMP links between the chiplets so each tile can share memory across the entire complex.

Here is the block diagram for the Zhejiang RISC-V chiplets:

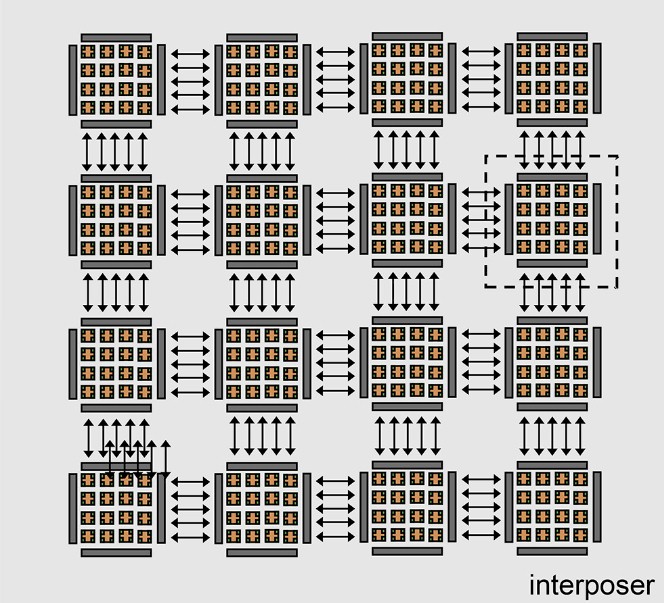

And here is how the die-to-die (D2D) interconnects are implemented using an interposer to lash 16 of these chiplets together into a 256-core compute complex with shared memory:

https://www.nextplatform.com/2024/01/03/with-big-chip-china-lays-out-aspirations-for-waferscale/There is absolutely nothing that prevents this chiplet design from being implemented as waferscale, and the CAS researchers said as much. However, for this iteration, it looks like it will be chiplets using a 2.5D interposer interconnect, which is probably all that SMIC can muster at this point.

Andes Announces General Availability of the New RISC-V Out-Of-Order Superscalar Multicore Processor, the AndesCore AX65

The AX65 is the first of the high-performance out-of-order AX60 series. Equipped with 13-stage pipeline, 4-wide decode, 8-wide out-of-order execution, AX65 targets the Linux application processor sockets of computing, networking, and high-end controllers.

Andes takes this opportunity to introduce the AX65 to complete its comprehensive CPU lineup, spanning from low-power embedded solutions to high-end Out-of-Order processors. Customers who develop complex SOC can now use AX65 as the primary Linux application processor, the AX45MPV/NX27V for the vector/DSP processing and the N25/N225 processors as the resource and power manager.

https://www.hpcwire.com/off-the-wir...calar-multicore-processor-the-andescore-ax65/The AX65 operates at speeds exceeding 2.0GHz on a 12nm process, boasting a SpecInt2006 score of 8.25 per GHz — outperforming the Cortex A75 with an efficient memory hierarchy. It also supports up to 8-core cache coherence with maximum 8MB shared cache. The AX65 is fully compliant with the RISC-V RVA22 profile, ensuring compatibility with operating systems and software within the RISC-V ecosystem. On the security side, AX65 supports Enhanced PMP (ePMP) for further securing memory accesses, and K (scalar cryptography) extension for accelerating AES and SHA crypto operations. For running Linux OS, the AX65 supports VIPT L1 instruction cache, SV48 virtual address space, and 2-level TLB with simultaneous hardware page walkers. It also incorporates state-of-the-art branch prediction mechanism with TAGE-L algorithm, return address stack and 2-level branch target buffer. The AX65 can be used as an application processor in networking applications like Wi-Fi, 5Gnr, and O-RAN, as well as in edge computing and industrial PCs. Furthermore, it is well-suited for serving as the primary controller processor in embedded applications.

MIPS Aims to Give Back Control, for AI-Centric Compute

This comes 40 years after the MIPS processor architecture was brought to market by MIPS Computer Systems, as it was known when John Hennesey, Chris Rowen, Skip (Edward) Stritter, and John Moussouris served as its founders, in 1984. Since then, MIPS went through several owners, and ultimately became independent in 2021. Soon after, the company announced a pivot to adopting RISC-V architecture going forward and launched two new IP cores based on RISC-V: the eVocore P8700 and I8500.

https://www.eetimes.com/mips-aims-to-give-back-control-for-ai-centric-compute/With Wasson stepping in as new CEO last year, and the announcement last week of two new executives to its leadership team, Drew Barbier and Brad Burgess (both previously at SiFive), MIPS felt now was the right time to create a “reset” in the brand, given its many ups and downs since being acquired by Imagination Technologies in 2013. Hence, at CES 2024, MIPS launched new branding reflecting its mission to give designers the freedom to innovate compute—and set out its general direction under Wasson.

Scaleway launches hosted RISC-V servers for 15.99 Euros per month

But the company has decided to try something new again with the EM-RV1 servers based on ***** T-Head TH1520 quad-core RISC-V processor, 16GB RAM, and 128GB eMMC flash and running Debian, Ubuntu, or Alpine.

672 RISC-V servers per 52U rack – Source: Twitter/X

EM-RV1-C4M16S128-A instance key features and specifications:

https://www.cnx-software.com/2024/03/01/scaleway-hosted-risc-v-servers/

- SoC – ***** T-Head TH1520

- CPU – Quad-core RISC-V Xuantie C910 (RV64GCV) processor @ 1.85 GHz

- GPU – Imagination BXM-4-64 with support for OpenCL 1.1/1.2/2.0, OpenGL ES 3.0/3.1/3.2, Vulkan 1.1/1.2, Android NN HAL

- VPU – H.265/H.264/VP9 video encoding/decoding

- NPU – 4 TOPS @ INT8 with support for TensorFlow, ONNX, Caffe

- System Memory – 16GB LPDDR4

- Storage – 128GB eMMC flash

- Networking – 100 *****/s Ethernet network card with public IPv4 and IPv6 addresses included

- Power Consumption – 0.96W to 1.9W per core @ ~1.8GHz; average: 1.3W per core

- Custom design with laser-cut chassis, 3D-printed blades

- Pricing – 0,042 € per hour, 15,99 € per month

Brasil e Europa assinam projeto inovador com Tecnologia RISC-V para HPC

Este projeto inovador marca o início da jornada destinada ao desenvolvimento de uma unidade de Aceleração para Multiplicação de Matrizes, integrada a um processador RISC-V. O principal objetivo é impulsionar os limites da computação de alto desempenho (HPC – High Performance Computing) e inteligência artificial.

A assinatura do Memorando de Entendimento consolida essa parceria entre o Instituto ELDORADO, com o apoio de pesquisadores da Universidade Estadual de Campinas (UNICAMP), e o Barcelona Supercomputing Center (BSC), um dos maiores centros europeus de supercomputação e pioneiro no desenvolvimento do padrão aberto RISC-V em chips.

https://www.eldorado.org.br/noticia...jeto-inovador-com-tecnologia-risc-v-para-hpc/A iniciativa faz parte do Programa Prioritário de Interesse Nacional PPI-Softex e está alinhada com o apoio do Ministério da Ciência, Tecnologia e Inovação (MCTI) no estabelecimento de parcerias tecnológicas entre o Brasil e a União Europeia, fortalecendo o intercâmbio de conhecimento e o suporte à excelência em pesquisa e desenvolvimento. Recentemente, o Brasil tornou-se Membro Premier da organização RISC-V Internacional, o que reforça o compromisso do país com o desenvolvimento tecnológico global.

BSC and Brazil’s Instituto ELDORADO Collaborate to Advance RISC-V Development for HPC and AI

https://www.hpcwire.com/off-the-wir...to-advance-risc-v-development-for-hpc-and-ai/The signing of the Memorandum of Understanding consolidates this partnership between Instituto ELDORADO, supported by researchers from the University of Campinas (UNICAMP), and the Barcelona Supercomputing Center – Centro Nacional de Superocmputación (BSC-CNS), one of the largest European supercomputing centers and a pioneer in the development of the open standard RISC-V in chips.