Intel’s Talks for Chip Designer SiFive Have Ended Without a Deal

Intel Corp.’s talks with chip designer

SiFive Inc. have ended without a deal and the startup will seek outside investment instead, according to people with knowledge of the matter.

Talks between the two companies fell apart recently after they couldn’t agree on financial terms and how the SiFive technology would be integrated into Intel’s chip roadmap, the people said, asking not to be identified because the matter is private.

SiFive is now looking to stay independent and sees an eventual initial public offering as a long-term goal, they said.

While the talks have ended, SiFive hasn’t ruled out eventually returning to discussions with Intel or other parties, the people added. The company had fielded takeover interest from Intel and other suitors earlier this year, Bloomberg News previously

reported.

Representatives for Santa Clara, California-based Intel and San Mateo, California-based SiFive declined to comment.

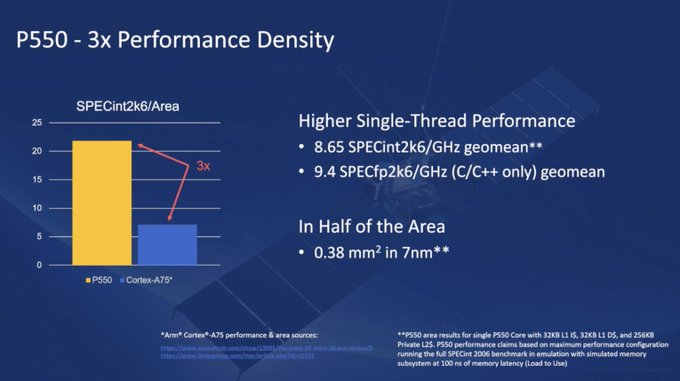

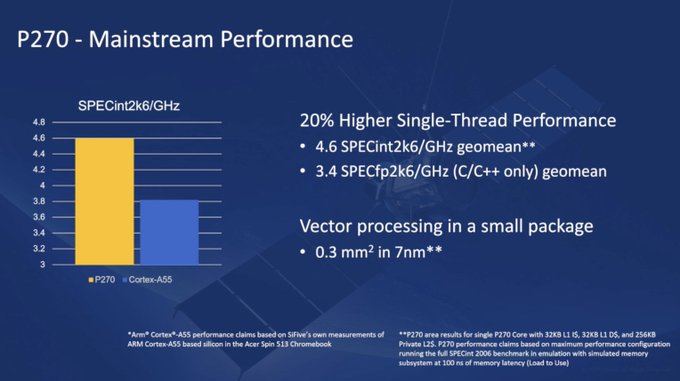

SiFive plans to increase hiring next month for its division that designs CPUs, or central processing units, one of the people said. The company aims to grow its CPU team from 200 to 400 employees. SiFive is working on chips that can compete with the high-end designs developed by Arm Ltd.

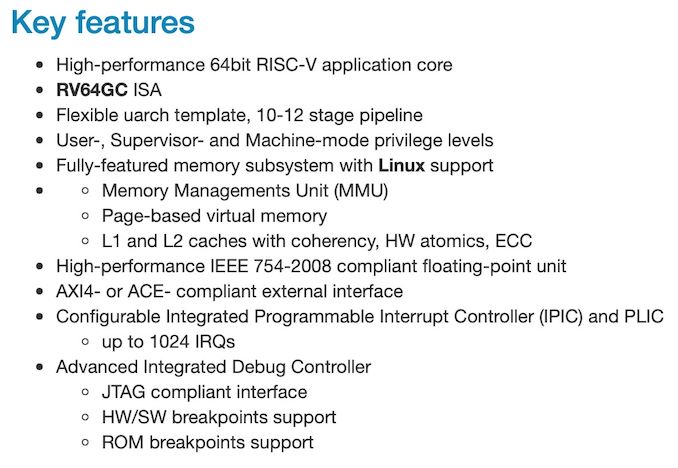

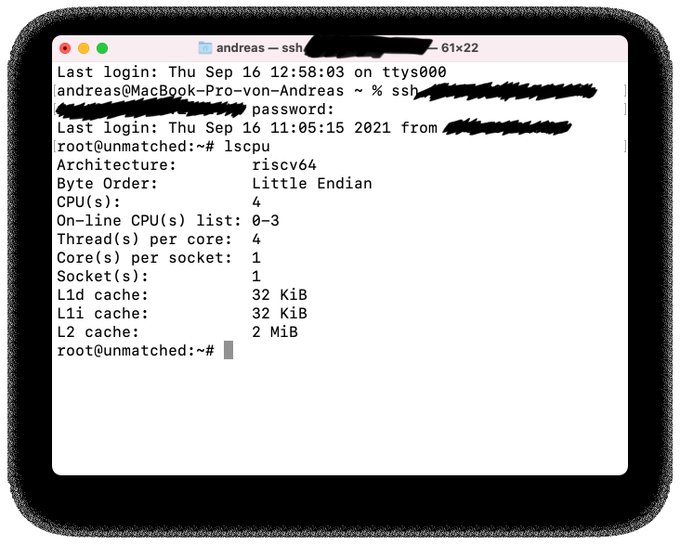

The chip industry is made up of two primary chip architectures: X86 and Arm. The X86 technology is currently used by Intel processors while Arm powers much of the mobile world including chips developed by Apple Inc. and Qualcomm Inc. SiFive is a leading developer of RISC-V technology, a newer architecture that’s starting to catch on.

RISC-V is seen as an attempt to bring open-source standards to chip designs, which could make such technology cheaper for chipmakers. Interest in SiFive increased after Nvidia Corp. announced a deal to buy Arm, which like SiFive, licenses chip and process designs. There are fears within the technology industry of Arm becoming less collaborative if its deal with Nvidia closes.

SiFive Chief Executive Officer Patrick Little is a chip industry veteran. He joined SiFive last year from Qualcomm Inc. where he was a senior vice president in charge of their automotive business.