Rafx

Power Member

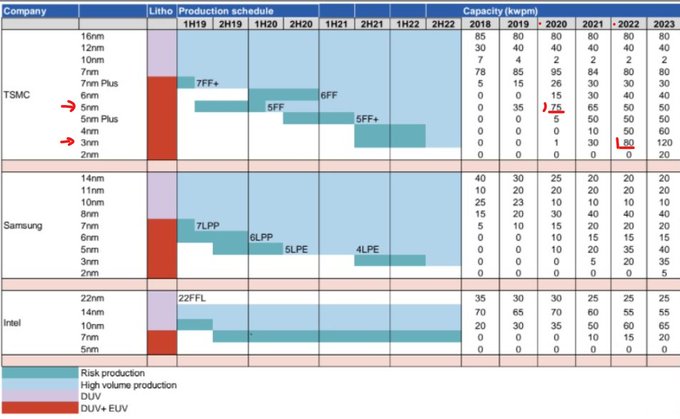

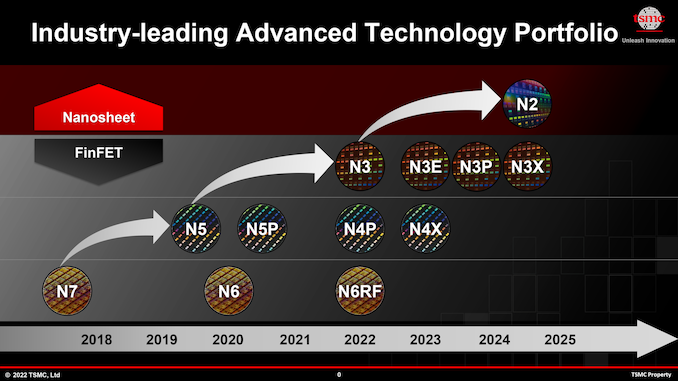

Ontem foi falado que os 5nm da TSMC estarão em produção em 2020, hoje é anunciado que os 3nm estarão prontos a produzir em 2022, um ano antes do projectado inicialmente (2023).

Esta noticia segue-se também ao facto da TSMC se ter tornado a empresa asiática mais valiosa, ultrapassando gigantes como a Samsung.

Se suceder como foi com os 7nm e como deve suceder com os 5nm, a AMD apresentará cpu's (Zen 6?) 3nm em 2023.

Para a AMD a nível de cpus consumidor o calendário deve ser:

2020: Zen 3, a 7nm 'optimizados' (7nm+?), ainda socketAM4

2021: Zen 4, a 5nm (+novo socket e ddr5)

2022: Zen 5, serão 5nm+/melhorados(?)

2023: Zen 6, 3nm

Isto a manter a cadência planeada de cpu's e a tendencia de uso de novos processos de fabrico no ano seguinte à estreia dos mesmos para a Apple.

Mesmo não tendo a estreia/bleeding edge logo que os novos processos estão a produzir, a AMD consegue manter uma cadência...tick-tock.

Conseguindo a TSMC realmente adiantar os 3nm para 2022, só mais más noticias a escalar para o lado da Intel..

Relembro que a Intel só terá 7nm prontos para 2021, mas que em 2021 a 7nm para consumidor só irá haver os novos gpu's discrete, portanto os primeiros cpu's 7nm da Intel só para 2022 a concorrer directamente com os 3nm da TSMC que hoje se falou.

Esta noticia segue-se também ao facto da TSMC se ter tornado a empresa asiática mais valiosa, ultrapassando gigantes como a Samsung.

fonteTSMC is delivering record results day after day, with a 5 nm manufacturing process starting High Volume Manufacturing (HVM) in Q2 next year, 7 nm process getting plenty of orders and the fact that TSMC just became the biggest company publicly trading in Asia. Continuing with the goal to match or even beat the famous Moore's Law, TSMC is already planning for future 3 nm node manufacturing, promised to start HVM as soon as 2022 arrives, according to JK Wang, TSMC's senior vice president of fab operations. Delivering 3 nm a whole year before originally planned in 2023, TSMC is working hard, with fab construction work doing quite well, judging by all the news that the company is releasing recently.

We can hope to see the first wave of products built using 3 nm manufacturing process sometime around end of year 2022, when the holiday season arrives. Usual customers like Apple and HiSilicon will surely utilize the new node and deliver their smartphones with 3 nm processors inside as soon as the process is ready for HVM.

Se suceder como foi com os 7nm e como deve suceder com os 5nm, a AMD apresentará cpu's (Zen 6?) 3nm em 2023.

Para a AMD a nível de cpus consumidor o calendário deve ser:

2020: Zen 3, a 7nm 'optimizados' (7nm+?), ainda socketAM4

2021: Zen 4, a 5nm (+novo socket e ddr5)

2022: Zen 5, serão 5nm+/melhorados(?)

2023: Zen 6, 3nm

Isto a manter a cadência planeada de cpu's e a tendencia de uso de novos processos de fabrico no ano seguinte à estreia dos mesmos para a Apple.

Mesmo não tendo a estreia/bleeding edge logo que os novos processos estão a produzir, a AMD consegue manter uma cadência...tick-tock.

Conseguindo a TSMC realmente adiantar os 3nm para 2022, só mais más noticias a escalar para o lado da Intel..

Relembro que a Intel só terá 7nm prontos para 2021, mas que em 2021 a 7nm para consumidor só irá haver os novos gpu's discrete, portanto os primeiros cpu's 7nm da Intel só para 2022 a concorrer directamente com os 3nm da TSMC que hoje se falou.

Última edição:

Se for escalar para o tamanho do CCD atual e arredondando para cima, temos 78mm2, 40 cores e 160 MB de Cache

Se for escalar para o tamanho do CCD atual e arredondando para cima, temos 78mm2, 40 cores e 160 MB de Cache

Provavelmente se virá as GPU a 3nm...

Provavelmente se virá as GPU a 3nm... para terem solução/alternativa que pelos vistos

para terem solução/alternativa que pelos vistos