Nemesis11

Power Member

Para quê andar a pensar se é melhor comprar DDR4 ou DDR5, quando vem aí DDR6?

Do Tech Day 2021 da Samsung.

DDR6:

LPDDR6:

GDDR7:

HBM3:

https://www-computerbase-de.transla...r_sl=de&_x_tr_tl=en&_x_tr_hl=bg&_x_tr_pto=nui

Do Tech Day 2021 da Samsung.

DDR6:

With DDR6 the doubling continues and for DDR6 up to 12,800 MT / s are planned accordingly, with DDR6 + it should be 17,000 MT / s. Samsung is working together with other JEDEC members from circles of DRAM and SoC manufacturers on the completion of the DDR6 standard, which according to current planning is expected in 2024. One of the chief engineers at SK Hynix had indicated in advance that it could take a little longer with this generation . Samsung now admits that it is still in the " early phase of development " of DDR6.

The number of memory channels (channel) per module is to increase to four with DDR6 and thus double again compared to DDR5. The number of memory banks increases by a factor of two to 64, which in turn means four times as much as DDR4.

LPDDR6:

At the same time, work is continuing on the more economical variant Low Power DDR (LPDDR) for mobile devices such as smartphones. Here LPDDR5 (up to 6,400 MT / s) or LPDDR5X (up to 8,500 MT / s) is the current state of development. Samsung already presented its new LPDDR5X last week . At the beginning of 2022, Samsung plans to mass-produce the LPDDR5X using the 1a-nm process.

In addition to more performance, the focus here is primarily on energy efficiency, which is improved with every generation. LPDDR6 should achieve up to 17,000 MT / s, but work another 20 percent more efficiently.

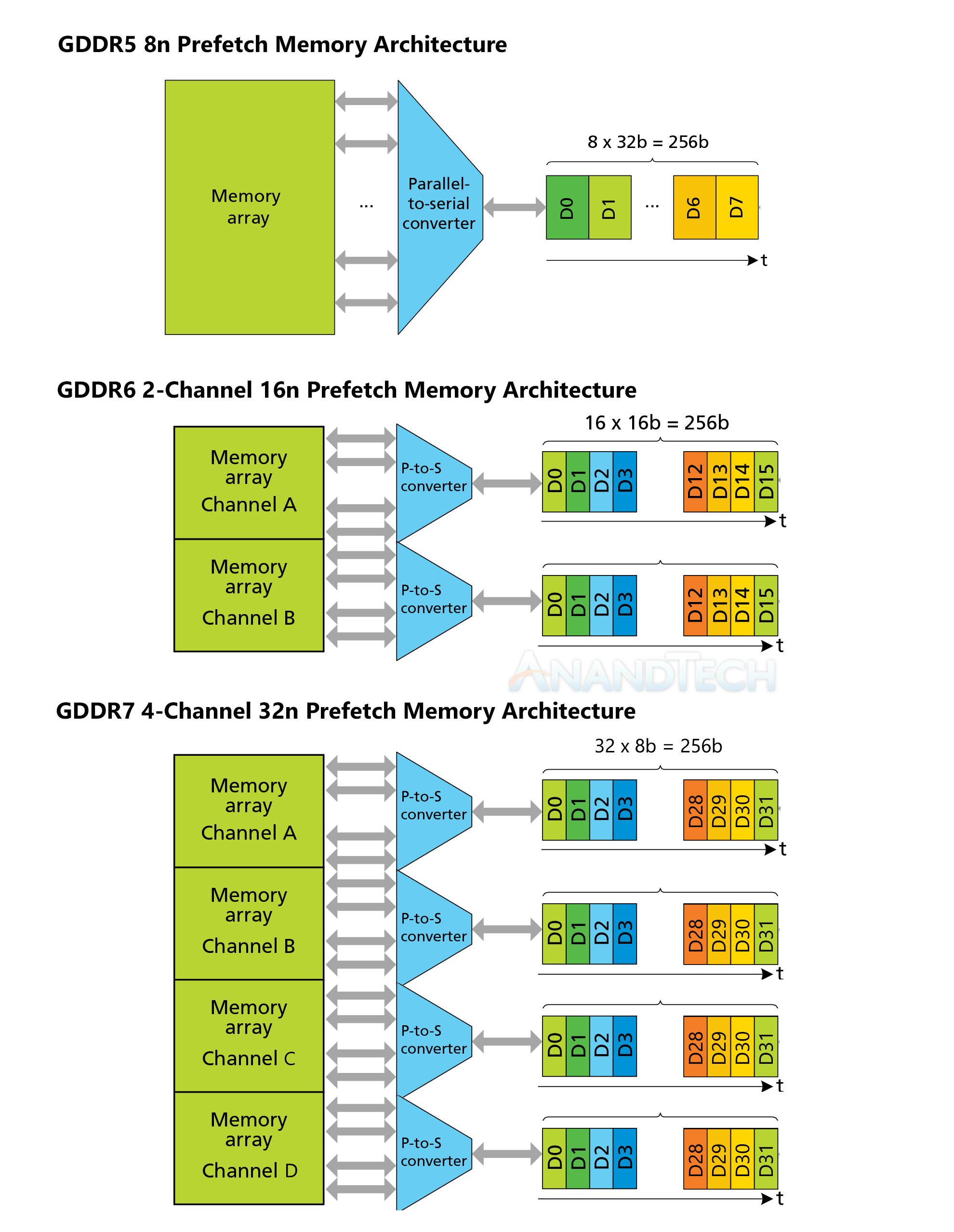

GDDR7:

Samsung describes its GDDR6 , which is primarily intended for graphics applications, with 18,000 MT / s as " currently the fastest DRAM in the world ". Samsung plans to increase this to 24,000 MT / s in the 1z nm process this month and is calling this level GDDR6 +. The successor GDDR7 is still on the roadmap without a public appointment. With this, the throughput should increase by a third to 32,000 MT / s. Another innovation in GDDR7 is a " real-time error protection feature ", which Samsung has not yet explained in more detail.

HBM3:

Just last month, SK Hynix announced the completion of its first HBM3 with 819 GByte / s , which will be used in products next year. The third generation of high-bandwidth memory , a DRAM variant trimmed for the highest transfer rates with stacked dies and short cable paths, is also on the agenda at Samsung. The manufacturer speaks of 800 GB / s for HBM3 and 450 GB / s for the intermediate level HBM2E. Samsung plans to mass-produce HBM3 in the second quarter of 2022 and emphasizes its suitability for AI applications.

https://www-computerbase-de.transla...r_sl=de&_x_tr_tl=en&_x_tr_hl=bg&_x_tr_pto=nui