Só 4 dimms por socket? Não aproveitam os 8 canais?

De qualquer forma, 512 núcleos de alta performance condensados nesse espaço...

Faça um zoom e consegues ver 8 DIMMs por socket

Estava a ver cada conjunto de 2 dimms e bloco de cooling dedicada a eles como um dimm. Habituado a dimms gordos xpto de desktop.

Estava a ver cada conjunto de 2 dimms e bloco de cooling dedicada a eles como um dimm. Habituado a dimms gordos xpto de desktop.Tem espaço ali naquela pseudo board para o socket gigante? ou serão Epyc soldados?

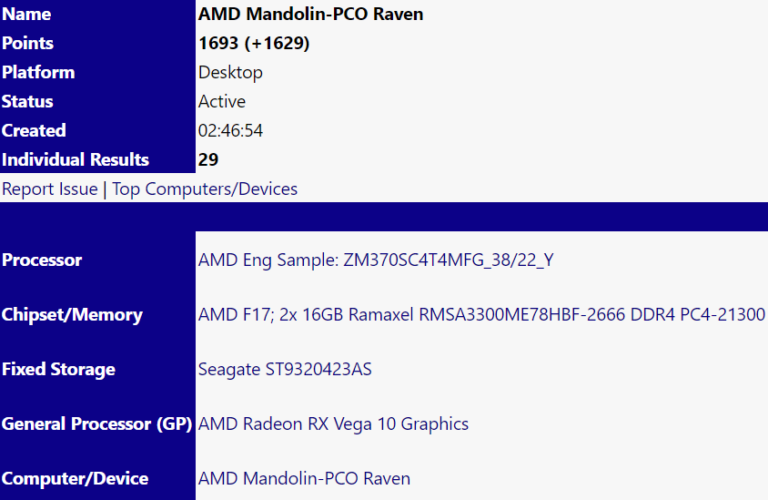

Only thing i can tell right now for specs is Ryzen 8 core, Price is 500$

PS VR 2 on the other hand will have no breaker box this time around it’ll be inside the console

No Breaker Box

Has a Camera (DS5 is going to have that too)

New Ps move controllers

They are also testing some gloves to go with the vr

The majority of the changes to the back-end involve the floating-point units. The most major change is the widening of the data path which has been doubled in width for the floating-point execution units. This includes the load/store operations as well as the FPUs. In Zen, AVX2 is fully supported through the use of two 128-bit micro-ops per instruction. Likewise, the load and store data paths were 128-bit wide. Every cycle, the FPU is capable of receiving 2 loads from the load/store unit, each up to 128 bits. In Zen 2, the data path is now 256 bits. Additionally, the execution units are now 256-bit wide as well, meaning 256-bit AVX operations no longer need to be cracked into two 128-bit micro-ops per instruction. With 2 256-bit FMAs, Zen 2 is capable of 16 FLOPS/cycle, matching that of Intel’s Skylake client core.

With eight octa-core compute dies, Rome can offer up to 64 cores and 128 threads, effectively doubling/quadrupling (AVX2) the throughput of first-generation EPYC. Although Rome stays with 128 PCIe lanes, it brings new supports for PCIe Gen 4, doubling the transfer rate from 8 GT/s to 16 GT/s. There are eight DDR4 memory channels supporting up to four terabytes of DRAM per socket. One interesting detail AMD disclosed with their GPU announcement is that the infinity fabric now supports 100 GB/s (BiDir) per link. If we assume the Infinity Fabric 2 still uses 16 differential pairs as with first-generation IF, it would mean the IF 2 now operates at 25 GT/s, identical to NVLink 2.0 data rate. However, since AMD’s IF is twice as wide, it provides twice the bandwidth per link over Nvidia’s NVLink.

One can see a design with four CPUs and four CPUs per sled. The GPUs are SXM2 NVIDIA Tesla cards. The CPUs appeared to be socket SP3 mounting patterns and AMD EPYC. We asked someone in the booth and received a yes nod when we asked if they were Hygon Dhyana.

https://www.servethehome.com/sugon-nebula-phase-change-immersion-cooling-a-unique-platform/Some of our US and European readers may not know Sugon. They are a large Chinese OEM vendor. You can see from our Top500 November 2018 New Systems Analysis that Sugon is a major HPC player capable of designing and delivering Top500 systems. Indeed, it has 57 of 500 systems on the November 2018 list.