Continuo na minha, um APU com mais de 300mm2 não parece viável para vender no segmento 50-150$. Um die monolitico deve ficar pelos 150-200 (dependendo se for 4 ou 8C e número de CUs

Onde?

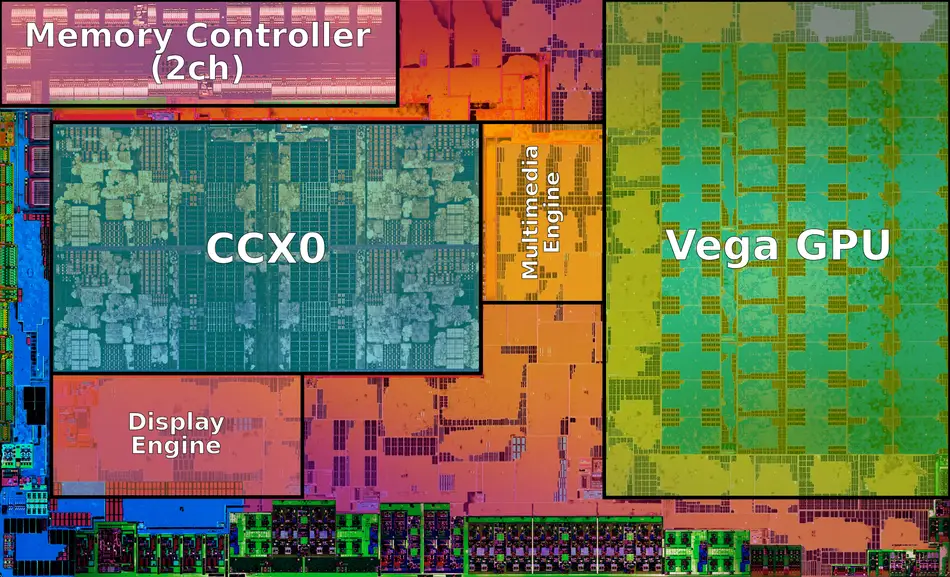

1 CCD Zen 2 = 80mm2 (7nm)

1 IOD Zen 2 = 125mm2 (12nm)

1 RX Vega 11 = 60mm2 (14nm)

Tudo somado = 265mm2

Isto assumindo que é usado exatamente o mesmo IOD dos Ryzen e um GPU idêntico ao usado no

3400G.

Além disso, não podemos esquecer que se os CCDs forem repescados, o custo do seu silício por mm2 será muitíssimo menor do que se for silício inteiramente novo para este CPU.

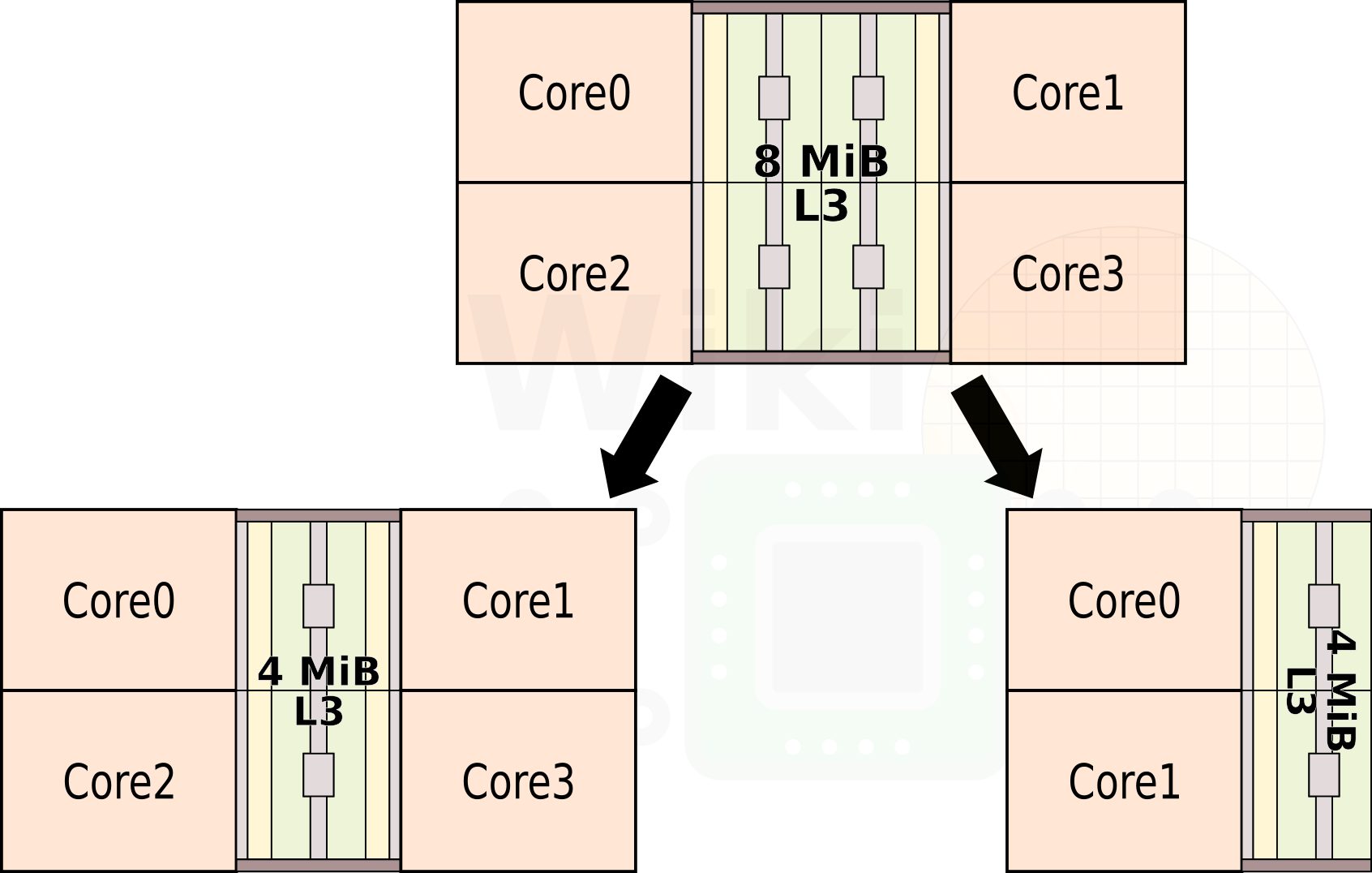

acumular CCDs de 2 e 4 cores, é mau ter que por questões de volume, ter que vender CPUs com cores bons cortados

Isto já tem lógica. Aliás, estou convencido que algo parecido aconteceu com o

3950X, que é provável que seja o único CPU de toda a gama que precisa do "top bin" (CCDs "perfeitos", isto é, com 8 cores muito bons).

Neste momento, penso que o pior bin de CCDs Zen 2 será o usado no EPYC 7262: 2 cores, base 3.1GHz e boost 3.3 GHz. Alguém que me corrija se estiver enganado. Tendo em conta que este EPYC é vendido 600 USD, a AMD deve estar a sacar uns 100 USD por cada CCD deste "bottom bin".

Mas deve haver bins ainda piores de CCDs Zen 2. Afinal o 300U (provavelmente o pior bin de Picasso) tem 2 cores, base 2.4 GHz e boost 3.3 GHz. Se há quem compra isto, também pode haver quem compre algo parecido baseado em Zen 2.

Para mim, o genial da estratégia dos chiplets é a AMD poder fazer apenas uma encomenda de CCDs à TMSC e com isso satisfazer toda a sua gama de CPUs, do mais barato ao mais caro. Não estou convencido que haja interesse em fazer algo completamente diferente para o Renoir quando é muito provável que tenham uma bin de CCDs mesmo à medida de um CPU desses.

Em comparação, um 3400G (o melhor bin de Picasso) tem 4 cores, base 3.7 GH e boost 4.2 GHz. Mas é um chip que só serve para essa gama. Resta saber se o volume de vendas dá para pagar os custos adicionais de R&D e fabrico de um chip Zen 2 dedicado a esta gama, especialmente tendo em consideração que o 3400G existe e já é muito competitivo.

A AMD tem um die para APU menor,

Mas foi isso que disse. Encolher e cortar é fácil. Mas esticar não. Como é que iam fazer um CCX de 6 cores?